Step logic models b

Found 11 free book(s)The Capital Asset Pricing Model: Theory and Evidence

mba.tuck.dartmouth.edualternative models. The Logic of the CAPM The CAPM builds on the model of portfolio choice developed by Harry Markowitz (1959). ... only portfolios above b along abc are mean-variance-efficient, since these ... The last step in the development of the …

Designing Education Projects - ERIC

files.eric.ed.govAppendix C. Logic Model and Performance Measures ... effective projects that can serve as models of excellence. Whether the project is an hour-long endangered species talk, a family festival, a severe weather awareness ... Education coordinators are encouraged to take a step back and make considered decisions that will result in increased ...

Study and Analysis of Various Decision Making Models in an ...

iosrjournals.orgThis model is based on logic of choice that would maximize the value and profitability of an organization [4]. According to this model, people follow a rationale method while making any decision. The sequences of various steps in this model are:- a. Identification of problem. b. Generation of solutions and alternatives.

PSIM User Manual - paginas.fe.up.pt

paginas.fe.up.pt7.1.1 Time Step Selection 7-1 7.1.2 Propagation Delays in Logic Circuits 7-1 7.1.3 Interface Between Power and Control Circuits 7-1 7.1.4 FFT Analysis 7-2 7.2 Error/Warning Messages 7-2 7.3 Debugging 7-4 Appendix A: Examples A-1 Appendix B: List of Elements B-1

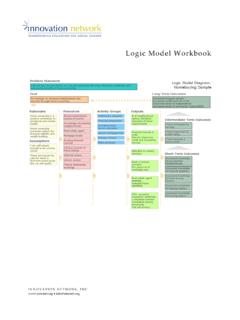

Logic Model Workbook - Innovation Network

www.pointk.organother programmatic area. We use the example of b ecoming a homeowner to give a more general conceptual framework. Problem Statement . The first step in creating a logic model is to clearly articulate the problem your work is tring to solve— that is, frame a particular challenge for the population you serve. problem that frames a

Basic circuit analysis - City U

cktse.eie.polyu.edu.hkStep 1: Define meshes and unknowns Each window is a mesh. Here, we have two meshes. For each one, we “imagine” a current circulating around it. So, we have two such currents, I1 and I2 — unknowns to be found. Step 2: Set up KVL equations Step 3: Simplify and solve which gives I1 = 6 A and I2 = 4 A. Once we know the mesh currents, we can

Basics of PLCs - Diagramasde.com

diagramas.diagramasde.com7 Siemens PLCs Siemens makes several PLC product lines in the SIMATIC® S7 family. They are: S7-200, S7-300, and S7-400. S7-200 The S7-200 is referred to as a micro PLC because of its small size. The S7-200 has a brick design which …

Syllabus for Scientist B 20201201 - National Institute of ...

apply-delhi.nielit.gov.inStream wise syllabus for Recruitment Exam for the Post of Scientist B (Electronics) 1. Engineering Mathematics Linear Algebra: Matrix Algebra, Systems of linear equations, Eigen values and Eigen vectors. Calculus: Mean value theorems, Theorems of integral calculus, Evaluation of definite and improper integrals, Partial Derivatives, Maxima and Minima, Multiple integrals, Fourier series, …

2.3 Bounds of sets of real numbers - Ohio State University

people.math.osu.edu0 < B 0 then a < B. Otherwise a 0 = B 0 and we go on to compare the first decimals. Either a 1 < B 1 therefore a < B or, otherwise, a 1 = B 1. Etc. So either a < B or a = B. So B is an upper bound. To show it is the least (upper bound), take any smaller number t < B. Then t differs from B at some first decimal, say at the nth decimal: t = B ...

California Common Core State Standards

www.cde.ca.govSenate Bill 1200, Statutes of 2012, called for modification of the California additions to the Common Core State Standards for Mathematics. The California Common Core State Standards: Mathematics (CA CCSSM) were modified January 16, 2013,

UltraFast Design Methodology Guide for the Vivado …

www.xilinx.comUltraFast Design Methodology Guide www.xilinx.com 6 UG949 (v2015.3) November 23, 2015 Chapter 1: Introduction Guide Applicability and References Although this guide is primarily for use with the Xilinx Vivado® Design Suite, most of the conceptual information in this guide can be leveraged for use with the Xilinx ISE® Design Suite as well.