Transcription of 1.5 On Resistance, ± 15 V / +12 V / ± 5 V, Quad …

1 DG1411E, DG1412E, Siliconix S18-0556-Rev. D, 11-Jun-20181 Document Number: 75104 For technical questions, contact: DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENTARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT On Resistance, 15 V / +12 V / 5 V, Quad SPST SwitchesDESCRIPTIONThe DG1411E, DG1412E, DG1413E are 15 V precisionmonolithic quad single-pole single-throw (SPST) CMOS analog switches. Built on a new CMOS process, the VishaySiliconix DG1411E, DG1412E, and DG1413E offer lowon-resistance of . The low and flat resistance over thefull signal range ensures excellent linearity and low signaldistortion.

2 The new CMOS platform provides low powerdissipation, minimized parasitic capacitance, and lowcharge devices operate from either a single V to 24 V powersupply, or from dual V to 15 V power supplies. Theanalog switches do not require a VL logic supply, while alldigital inputs have V and 2 V logic thresholds to ensurelow voltage TTL / CMOS compatibility. The DG1411E, DG1412E, and DG1413E are bi-directionaland support analog signals up to the supply voltage whenon, and block them when off. The devices each feature fourindependently selectable SPST switches. The DG1411E isnormally closed, while the DG1412E is normally open. TheDG1413E has two normally open and two normally closedswitches with guaranteed break-before-make operation.

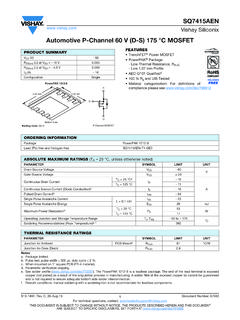

3 Combined with fast 70 ns switching time, low and flat switchresistance. The devices are ideal for signal switching andrelay replacement in data acquisition, industrial control andautomation, communication, and A/V systems, in addition tomedical instrumentation and automated test switches are available in RoHS-compliant, halogen-freeTSSOP16 and QFN16 4 mm by 4 mm 35 V supply max. rating On-resistance: On-resistance flatness: Channel to channel on-resistance match: Supports single and dual supply operation Fully specified at 15 V, 5 V, and +12 V Integrated VL supply 3 V logic compatible Low parasitic capacitance: CS(OFF): 24 pF, CD(ON): 87 pF Rail to rail signal handling Material categorization.

4 For definitions of complianceplease see Low insertion loss Low distortion Break-before-make switching Low charge injection over the full signal rangeAPPLICATIONS Medical and healthcare equipment Data acquisition system Industrial control and automation Test and measurement equipment Communication systems Battery powered systems Sample and hold circuits Audio and video signal switching Relay replacementFUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION - DG1411 ENotes QFN exposed pad tied to V- = no connect Switches shown for logic 0 inputTRUTH TABLE - DG1411 ELOGICSWITCH0On1 OffDG1411 EENV-V+ p V i e wQFN-16 (4 mm x 4 mm)D1IN1IN2D2D4IN4IN3D312345678161514131 211109 Top ViewIN1IN2D1D2S1S2V-V+ , DG1412E, Siliconix S18-0556-Rev.

5 D, 11-Jun-20182 Document Number: 75104 For technical questions, contact: DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENTARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT BLOCK DIAGRAM AND PIN CONFIGURATION - DG1412 ENotes QFN exposed pad tied to V- = no connect Switches shown for logic 0 inputFUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION - DG1413 ENotes QFN exposed pad tied to V- = no connect Switches shown for logic 0 inputTRUTH TABLE - DG1412 ELOGICSWITCH0 Off1 OnDG1412 EENV-V+ p V i e wQFN-16 (4 mm x 4 mm)D1IN1IN2D2D4IN4IN3D312345678161514131 211109 Top ViewIN1IN2D1D2S1S2V-V+ TABLE - DG1413 ELOGICSWITCHES 1, 4 SWITCHES 2, 30 OffOn1 OnOffDG1413 EENV-V+ ViewQFN-16 (4 mm x 4 mm)

6 D1IN1IN2D2D4IN4IN3D312345678161514131211 109 Top ViewIN1IN2D1D2S1S2V-V+ , DG1412E, Siliconix S18-0556-Rev. D, 11-Jun-20183 Document Number: 75104 For technical questions, contact: DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENTARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operationof the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximumrating conditions for extended periods may affect device OPTIONSPART NUMBERCONFIGURATIONSWITCHFUNCTIONTEMPERA TURE RANGEPACKAGEDG1411 EEN-T1-GE4 Quad SPSTNC-40 C to +125 CQFN (4 mm x 4 mm) 16L (variation 2)DG1412 EEN-T1-GE4 Quad SPSTNO-40 C to +125 CQFN (4 mm x 4 mm) 16L (variation 2)DG1413 EEN-T1-GE4 Quad SPSTNC / NO-40 C to +125 CQFN (4 mm x 4 mm) 16L (variation 2)

7 DG1411 EEQ-T1-GE4 Quad SPSTNC-40 C to +125 CTSSOP-16DG1412 EEQ-T1-GE4 Quad SPSTNO-40 C to +125 CTSSOP-16DG1413 EEQ-T1-GE4 Quad SPSTNC / NO-40 C to +125 CTSSOP-16 ABSOLUTE MAXIMUM RATINGSELECTRICAL PARAMETER CONDITIONSLIMITSUNITV+Reference to to +25V V-Reference to GND+ to -25V+ to V-+35 Analog inputs (S or D)(V-) - to (V+) + inputsGND - to (V+) + continuous switch currentTSSOP-16, TA = 25 C190mAQFN (4 mm x 4 mm) 16L, TA = 25 C250 TSSOP-16, TA = 125 C90 QFN (4 mm x 4 mm) 16L, TA = 125 C100 Maximum pulse switch currentPulse at 1 ms, 10 % duty cycle500 Thermal resistanceTSSOP-16130 C/WQFN (4 mm x 4 mm) 16L32 ESD / HBMJS-0012000 VESD / CDMJS-002750 Latch upJESD78300mATemperatureOperating temperature-40 to +125 CMax.

8 Operating junction temperature150 Operating junction temperature125 Storage temperature-65 to +150DG1411E, DG1412E, Siliconix S18-0556-Rev. D, 11-Jun-20184 Document Number: 75104 For technical questions, contact: DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENTARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT CHARACTERISTICS - 15 V supplyPARAMETER SYMBOLTEST CONDITIONSUNLESS OTHERWISE SPECIFIEDV+ = 15 V, V- = -15 VVINH = 2 V, VINL = V+25 C-40 C to +85 C-40 C to +125 CTYP. / SwitchAnalog signal rangeVANALOGV- to V+-V Drain-source on-resistanceRDS(on)VS = 10 V, IS = -10 mAV+ = V, V- = flatnessRflat(on)VS = 10 V, IS = -10 matching RDS(on) off leakage currentIS/Id(off) V+ = V, V- = VVS = 10 V, VD = 10 V 2 on leakage currentId(on)

9 VS = VD = 10 V 1 3 ControlInput, high voltageVINH-- 2 , low voltageVINL-- leakage IINVIN = VGND or V+ A -- input capacitanceCIN CharacteristicsBreak-before-make timetOPENVS1= VS2 = 10 V RL= 300 , CL = 35 timetONVS = 10 VRL = 300 , CL = 35 injectionQINjCL = 1 nF, RGEN = 0 , VS = 0 isolationOIRRCL = 5 pF, RL = 50 , 100 talkXTALKCL = 5 pF, RL = 50 , 1 lossf = 1 MHz, RL = 50 , CL = 5 harmonic distortionTHDRL = 110 , 15 Vp-p, f = 20 Hz to 20 , -3 dBBWCL = 5 pF, RL = 50 off capacitanceCS(off)f = 1 MHz, VS = 0 off capacitanceCD(off) on capacitanceCD(on) RequirementsPower supply rangeGND = 0 V V min.

10 / supply currentI+Digital inputs 0 or V+V+ = V, V- = A-- = IN2 = IN3 = IN4 = 5 inputs 0 or V+ 1 Max. DG1411E, DG1412E, Siliconix S18-0556-Rev. D, 11-Jun-20185 Document Number: 75104 For technical questions, contact: DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENTARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT CHARACTERISTICS - Single 12 V supplyPARAMETER SYMBOLTEST CONDITIONSUNLESS OTHERWISE SPECIFIEDV+ = 12 V, V- = -0 VVINH = 2 V, VINL = V+25 C-40 C to +85 C-40 C to +125 CTYP. / SwitchAnalog signal rangeVANALOG0 to V+V Drain-source on-resistanceRDS(on)VS = 0 V to 10 V, IS = -10 mA;V+ = V, V- = 0 flatnessRflat(on)VS = 0 V to 10 V; IS = -10 matching RDS(on) off leakage currentIS/Id(off) V+ = V, V- = 0 VVS = 1 V/10 V.