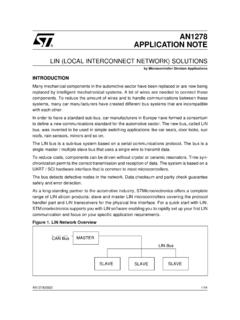

Transcription of MCS@51 MICROCONTROLLER FAMILY USER’S …

1 MCS@51 MICROCONTROLLERFAMILYUSER SMANUALORDERNO. , sFASTPATH arenotaffiliatedwithKinetics,adivisionof Excelan, ,lOfherbrandsandnamesaretheproperlyofthe irrespectiveowners, ,IL6005S-7641orcall1-800-879-4683c-INTEL CORPORATION,1093 MCS 51 CONTENTSPAGEMICROCONTROLLERc *pTf==1 FAMILYMCS51 FamilyofMicrocontrollersUSER , @ .. @ -51 MemoryStructureCHMOSD evicesFunctionally,theCHMOS devices(designatedwith C inthemiddleofthedevicename)meallfiuycomp atiblewiththe8051,butbeingCMOS, ,twore-ducedpowermodesareaddedlSoftware- invokedIdleMode, ,cur-rentdrawisreducedtoabout15% , ,s~ , -51 ProgramMemoryTheinterruptaeMcelocationsa respacedat8-bytein-tervak0U03 HforExternalInterruptO,000 BHforTmerO,0013 HforExternalInterrupt1,00 IBHforTimer1, (asisoftenthecaseincontrolapplications), , (orSKor16K) ~(Ex-ternalAccess)

2 ,ifthe=pinisstrappedtoVcC, ,==Vccselectsad-dresses(XtOOHthroughlFFF H tobeinternal,andad-dresses2000 HthroughF ,==VCCselectsad-dresses0000 Hthrough3 FFFH tobeinternal, ~pinisstrappedtoVss, :PSEN, sl==m%1 Pom= s ,theOtherBitsofP2areAvailableas1 , ,irzwhichcasethehighaddressbyteisemitted atPort2.~:.. ,AC=IELEACCESSIBLEUPP~,SVINDIREC7 BVOIRECT:AtORESSINGAODRSSSINGONLYSDH980H mACCESSIBLELOWERSY01 REC7 SPWAL128 ANOINC+REC71 WNC710N&oAmm~ooAGGRESSING E~mCONTROLemsTIMERRE STACKiolN7 ERACCUMULATOR( nC.) ,whicharegenerallyreferredtoastheLower12 8,theUpper128, ,theaddressingmodesforintemsslRAMeaninfa ctseeommodate384bytes, , ~FFH,slthoudtheyarephysi-callyseparateen tities;n7 FHBANKIll2 FHSELECTBRSIN1SN-ACORESSASLSSPACE(S~A~ES SESO-7F) 120H {lSH1FH 0{10H17H4 SANKSOF8 REGIS7 SRS0 @-51 ARCHITECTURALOVERVIEWCTIAC]FOIRSIIRBO[OV IIPIbaaA*ACARRYFLAGRECEIVESCMi/fmw.)}}

3 1 KWOPARllYOFACCLWUIATORSS7 FROUBIT1 OfALUOPERANOS~NARoWARCTO1 IFITCONTAINSAN000 NUMBEROF1S,OTHERWISE171 SRESE7TO0 Psw6 Psw1 AUXILIARYCARRYFLAGRECEIVESCARRYOUTFROMB1 71 OFUSEROEFINABLEFUGAOOMONOPERANOSnw5 Psw2 GENERALPURPOSES7 ATUSFLAGOVERFLOWFIAOSETBYARITIMCWOPERAl! ONSREGtS7 ERBANKSW % (Progrsmssssusworn)Registermmc5w-51t2evt cesThenext16byteaabovetheregisterbankBfo rmablock!% , ) (Figure8) ,butmeinthedeviceswith256byteaofRAM.(SeT able1).Figure9givesabrieflookattheSpecia lFunotionReg-ister(SFR) ,tim-ers,pe2iphAcontrols, ,allMCS-51microcontrollershavethesameSFR B asthe8051, ,enhance-mentstothe8051haveadditionalSFR B thatarenotpresentinthe8051,norperhapsino therproliferationsofthefamily.

4 URE~MAPPSOPOR7 SEOHmAOORESSES7 NATENDINOHORENARCALSOB~ (E7c.) theassembler inthisdiscussionaretoIntel sMCS-51 MacroAssembler, sGuide( , ).ProgramStatusWordTheProgramStatusWord( PSW) ,showninFigure10, ~theAuxdiaryCarry(forBCDoper-ations),the tworegisterbankselectbits,theGvesflowfla g,aParitybit, ,otherthanservingthefunctionsofaCarrybit inarithmeticoperations,alsoseswsasthe Accumulator datapointer register, ,containingregistersROthroughR7, , ,someinstructionsalwaysoperateontheAc-cu mulator,orDataPointer,etc., ,MOVA,# , (eitherDPTR ortheProgramCounter)pointstothebaseofthe table, casejump @-51 ARCHITECTURALOVERVIEWT able2 AUstoftheMCS@I-51 ArithmeticInstructionsMnemonicOperationA ddressingModesExecutionDkIIndRqlmmTime(@ ADDA,<byte>A=A+<byte>xxxx1 IADDOA,<byte>IA=A+<byte>+CIXIXIXIX]1 ISUBBA,<byte>A=A <byte>-Cxxxx1 INCAIA=A+lIAccumulatoronlvI1 IINC.)

5 <byte>I<byte>=<byte>+lIXIXIXI11-1 IlhJCDPTRIDPTR=DpTR+1 IDataPointeronly121 IDECAIA=A-lIAccumulatoronlyIllDEC<byte> <byte>=<byte> [A/B]B=MOd[A/BlACCandBonlyI4 IIDAAID ecimalAdjustIAccumulatoronlyIllTheDIVAB instructiondividestheAccumulatorbythedat aintheBregisterandleeveathe8-bitquotient intheAccumulator, ,DIVAB findsleesuseinarithmetic divide @ SP ,<src>x2 POP<dest>MOV<dest>, @SP :DECSPx2 XCHA,<byte>ACCand<byte>exchangedataxxx1 XCHDA,@RiACCand@ @Rl001234567876 XCHDA,@ @ @-51 DataTrsnaferInstructionsthatAcceesExtarn slDataMemorySpaoeAddressMnemonicOperatio nExecutionWidthTime(*)8b~MOVXA,@ RiReadexternal~RAM@Ri8bbMOVX@Ri,AWriteex ternalRAM@Ri2 Readexternal 6bns ovx @DpTRRAM@DPTR216bfiaWritaexlemal ovx DmR renotgoingtobeusedatutheirpinsareavail-a bleasextra1 ,thelookuptableacanonlyberead, moveconstant.]

6 IfthetableaccessistoexternalProgramMemor y, TABLE scomplement)oftketbytewhichisaddedtotheP Cintwo -51 OavicesIMnarnonicIOperationExeeutionTiln a(us)IJMP addrIJumotoaddr121 JMP@A+DPTRIJ umptoA+DPTRI2 CALL addrICallsubroutineataddr21 RETIR eturnfromsubroutineIzIIRETIIR eturnfrominterruptI2 INOPN ooparation1 TheTablelistsasingle JMPaddr instruction,butinfacttherearethree-SJMP, , , + , ,eonaistingoftheopode,whichitselfcontain s3ofthe11addressbits, , ,a Destinationoutofrange @A+DPTRTheRLAinstructionconvertstheindex number(Othrough4)toanevennumberontherang eOthrough8,becauseeachentryinthejumptabl eis2byteelong:~P_TABLEMMPCASE_OAJMPCASE_ lAJMPCASE_2 AJMPCASE_3 CASE_4 Table8showsasingle CALL addr instruction, , , , , ~andsoarelindtedtoajumpdistanceof great=than,lessthan ,thentheCarrybitisset(l).

7 Ifthefirstisgreaterthanorequaltothesecon d, ,connectacrystalorceramicresonatorbetwee ntheXTAL1andXTAL2pinsofthemicrocontrolle r,andcapacitorstogroundasshowninFigure13 .@ > %HMOSORC nuosSmLSCLOCKSTAL1 SIGNAL= -51 HMOSEilSRNALONLYCLOCKSTAL2 STAL1 Vss= !CHMOSONLY(w) ~.MCS 5 (S051,etc.)thesignalattheXTAL2pinAmachin ecycleconsistsofasequenceof6statea, (SOC5lBH,ete.) , (%L)IIALE1J! :,,-4ir-NEmo READOPCOOE(MWX).READNEXTNOIOPCOOE(OISCAR D), 1= ,,;II~NOALE1~------sla2a2s4]aseelS11S21S 2] [0)MOW(l-,S-c@ @ tneedmorecodebytes,theCPUsimplyignoresth eextrafetch, (Figure15 AandB) , (D). ~xternsl,thentheProgramMemo-ryreadstrobe PSEN isnormallyactivatedtwicepermachinecycle, asshowninFigure16(A).

8 IfanaccesstoexternalDataMemoryoccurs,ass howninFigure16(B),twoPSENS areskippe$ , [a21s21s41aslssSIIS21S21S41SE126 ALEIII1!,-N~III11 ILrI1I11 IIIro1 III11 WITH%) [PCHOUTx IPCNOUT1II1t~::$mt5i:Fty;LL&T&TG:v:m @ I IESIETIIEXIIETOIEXOE nablebk= , ,eachintenuptsourceisitiiuslfyenabledord isebledbysettingwclearingiteeneblebit. ! (InterruptEnable)Registerinthe8051natned IE(InterruptEnable).Thisregisteralsocon- tainsaglobaldisablebit, ~edt?oneoftwoprioritylevelsbysettingorcl earingabltmtheSFRnamed1P(InterruptPriori ty). , , , ,forthe8051,howtheIEandIPregie-tersandth epollingsequenceworktodeterminewhichifan yinttiptWiilbe-serviced.]]

9 (MSB)(LSB) IPSIPTIIPXIIPTOIPXOP rforifybit= + POLUNGINTERRUPT1 SEQUENCEol-& :0b7 FIJ&oII:0 vRInJ+IA\~ (l),theinterruptsystemgeneratesanLCALL totheappropriatelocationinProgramMemo-ry , , , (Rgare3), , ,albdtattheexpenseofincreasingthepro--er sbu~ ,manysnterruptfunctionsthataretypicalinc ontrolapplics-tions-togghmgaportpimforex ample,orreloadingatimer,orunloadingaseri albut% , ,interruptsthataretohavehigherpriorityth an1aressaignedtopriority1inthe1P(Interru ptPriority) priority2 interruptsarewrittentoincludethefollowin gcodePUSHIEMOVIE,#MASKCALLLABELl**(execu teserviceroutine)l**POPIERETLABELRETI1-2 1 MCS@I-51 ARCHITECTURALOVERVIEWA ssoonasanypriority1interruptisacknowledg ed,theIE(InterruptEnable)

10 Registerism-definedsoastodisableallbut priority2 ,aCALLtoLAEEL exeoutestheRETI instruction, ,butOdy priority 2 (ratherthananotherRETI) (at12 MHz) (OrderNum-ber:270648) UsingtheIntelMCW-51 BooleanProcess-ingCapabtities 1-22 MCS@51 Programmer s2 GuideandInstructionSetMCWI51 PROGRAMMER ,..,.. ,..,, ,..,..,.. ,.., ,..,.,,..2-13 ,.2-14 ,..,..,..,.,..2-15 ,.. ER AL ORT N ODE2.. - - .. ;- ~.MCS@-51 PROGRAMMER SGUIDEANDINSTRUCTIONSETT heinformationpreaentedinthischapteriscol lectedfromtheMCW-51 ArchitecturalOverviewandtheHardwareDescr iptionofthe8051, , (8 Kforthe8052) , @-51 PROGRAMMER SGUIDEANDINSTRUCTIONSETS4 KBWEB270249-2 -51 PROGRAMMER SGUIDEANDINSTRUCTIONSETOFFF F9 IDIRECT&INomECTAoon~ rEmALIWIRECT6 ADORESSINGONLYemToFFnw emaOmE( ~.)