Search results with tag "Fixed point"

2.2 Fixed-Point Iteration - University of Notre Dame

www3.nd.edu• A number is a fixed point for a given function if = • Root finding =0 is related to fixed-point iteration = –Given a root-finding problem =0, there are many with fixed points at : Example: ≔ − ≔ +3 … If has fixed point at , then = − ( ) has

Lecture 9: Digital Signal Processors: Applications and ...

bwrcs.eecs.berkeley.eduDSP Data Path: Precision Word size affects precision of fixed point numbers DSPs have 16-bit, 20-bit, or 24-bit data words Floating Point DSPs cost 2X - 4X vs. fixed point, slower than fixed point DSP programmers will scale values inside code SW Libraries Separate explicit exponent

Floating point to Fixed point conversion - Sharif

ee.sharif.eduFixed‐Point Design 3 Where: > Ü is the ith binary digit S H is the word length in bits > ê ß ? 5 is the location of the most significant, or highest, bit (MSB) > 4 is the location of the least significant, or lowest, bit (LSB). The binary point is shown three places to the left of the LSB.

This Unit: Floating Point Arithmetic

www.cis.upenn.edu•Many embedded chips today lack floating point hardware •Programmers built scale factors into programs •Large constant multiplier turns all FP numbers to integers •inputs multiplied by scale factor manually •Outputs divided by scale factor manually •Sometimes called fixed point arithmetic CIS371 (Roth/Martin): Floating Point 6

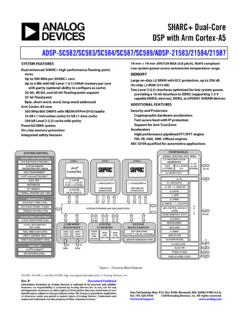

SHARC+ Dual-Core DSP with Arm Cortex-A5

www.analog.comDual enhanced SHARC+ high performance floating-point cores Up to 500 MHz per SHARC+ core Up to 5 Mb (640 kB) Level 1 (L1) SRAM memory per core with parity (optional ability to configure as cache) 32-bit, 40-bit, and 64-bit floating-point support 32-bit fixed point Byte, short-word, word, long-word addressed Arm Cortex-A5 core

Fix Point Implementation of ClAlihControl …

www.artist-embedded.orgOutline • A-D and D-A Quantization • Computer arithmetic –Floating-point arithmetic –Fixed-point arithmetic • Controller realizations Graduate Course on Embedded Control Systems – Pisa 8-12 June 2009

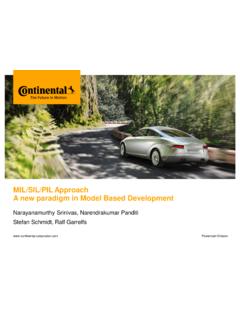

Mil-Sil-Pil A New Paradigm in Model-Based Development

www.mathworks.comFLP : Floating point model FXP : Fixed point model MvS: Model verifiedby Simulation SIL : Software In the Loop PIL : Processor In the Loop HIL: Hardware In the Loop TVG : Test Vector Generation Require-SYSTEM ments Implemen-tation Model (FXP) Physical Model (FLP) Automatic Code Generation SIL PIL Module Test Validation HIL Car Integration Test ...

Digital Signal Processor (DSP) Architecture

meseec.ce.rit.eduOct 08, 2003 · Digital Signal Processor (DSP) Architecture ... TYPES OF DSP PROCESSORS • 32-BIT FLOATING POINT (5% of market): – TI TMS320C3X, TMS320C67xx – AT&T DSP32C – ANALOG DEVICES ADSP21xxx – Hitachi SH-4 • 16-BIT FIXED POINT (95% of market):

Math 131: Introduction to Topology 1

people.math.harvard.edu11/6/2019 - The Brouwer Fixed Point Theorem85 11/11/2019 - Antipodes and the Borsuk-Ulam Theorem88 11/13/2019 - Deformation Retracts and Homotopy Equivalence91 11/18/2019 - Computing the Fundamental Group95 11/20/2019 - Equivalence of Covering Spaces and the Universal Cover99 11/25/2019 - Universal Covering Spaces, Free Groups104

Value Function Iteration - University of Pennsylvania ...

www.sas.upenn.edu• The function V is the fixed point to this functional equation. 12. The Bellman equation in the infinite horizon problem II • To determine existence and uniqueness, we need to impose: 1. S and A are compact metric spaces. ... Value function iteration ...

Fixed-Point Arithmetic: An Introduction

courses.cs.washington.edunumbers are simple signed two’s complement integers. Contrast this against the Motorola 56k series which performs two’s complement fractional arithmetic, with values always in the range −1≤ x < +1. It is my hope that this material is clear, accurate, and helpful. If you find any errors or inconsistencies, please email me at yates@ieee.org.