Search results with tag "Noise immunity"

EXPERIMENT 3: TTL AND CMOS CHARACTERISTICS

www.classe.cornell.eduNoise immunity is a measure of the ability of a digital circuit to avert logic level changes on signal lines when noise causes voltage level changes. (See Figure 3.3.) One measure of noise immunity is characterized by a pair of parameters: the dc HIGH and LOW noise margins, DC1 and DC0, respectively. They are defined as follows:

High noise immunity 74HC4053; 74HCT4053 • JESD8C (2.7 V …

assets.nexperia.com• High noise immunity • Latch-up performance exceeds 100 mA per JESD78 Class II Level B • Complies with JEDEC standard: • JESD8C (2.7 V to 3.6 V) • JESD7A (2.0 V to 6.0 V) • Low ON resistance: • 80 Ω (typical) at VCC - VEE = 4.5 V • 70 Ω (typical) at VCC - VEE = 6.0 V • 60 Ω (typical) at VCC - VEE = 9.0 V

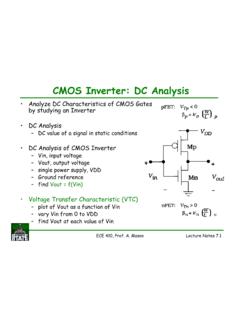

CMOS Inverter: DC Analysis - Michigan State University

www.egr.msu.edu• Voltage Noise Margins – measure of how stable inputs are with respect to signal interference –VNM H = V OH-V IH = VDD - V IH –VNM L = V IL-V OL = V IL – desire large VNM H and VNM L for best noise immunity =− 1 ∂ ∂ Vout Vin

Phase Locked Loops (PLL) and Frequency Synthesis

rfic.eecs.berkeley.edufaster than CMOS, and has superior noise immunity and generation due to the di erential nature. Injection locked or TSPC dividers are also useful for very low power high frequency operation. Niknejad PLLs and Frequency Synthesis