VHDL Reference Manual

• Dataflow VHDL • Behavioral VHDL • Structural VHDL. Language Structure 2-2 VHDL Reference Manual ... A design may include any number of package, entity, architecture, and configuration declarations. The relationship of the four types of design units is illustrated in Figure 2-2. Note that only the entity and

Download VHDL Reference Manual

Information

Domain:

Source:

Link to this page:

Please notify us if you found a problem with this document:

Documents from same domain

STATISTICS 8 CHAPTERS 1 TO 6, SAMPLE …

www.ics.uci.eduSTATISTICS 8 CHAPTERS 1 TO 6, SAMPLE MULTIPLE CHOICE QUESTIONS ... a student who scored 0 on the final exam would be predicted to score 50 on the midterm

Question, Exams, Multiple, Chapter, Statistics, Samples, Final, Choice, Final exam, Statistics 8 chapters 1 to 6, Sample multiple choice questions

EAC COMMISSION - University of California, Irvine

www.ics.uci.edu2015-2016 Criteria for Accrediting Programs EAC COMMISSION General Criteria 3. Student Outcomes (a) ... 2010-2011 Criteria for Accrediting Computing Programs.

Computing, Commission, Criteria, Accrediting, Criteria for accrediting, Criteria for accrediting computing, Eac commission

Biostatistics A sample of questions for the nal exam

www.ics.uci.eduA sample of questions for the nal exam 1. Consider the following two plots. Write down these probabilities: Consider the following two plots. Write down these probabilities:

Question, Samples, Biostatistics, Biostatistics a sample of questions

Sensor Networks: Evolution, Opportunities, and …

www.ics.uci.eduSensor Networks: Evolution, Opportunities, and Challenges CHEE-YEE CHONG, MEMBER, IEEE AND SRIKANTA P. KUMAR, SENIOR MEMBER, IEEE Invited Paper Wireless microsensor networks have been identified as one of

Network, Challenges, Opportunities, And challenges, Sensor, Evolution, Sensor networks

A Validation Fault Model for Timing …

www.ics.uci.eduA Validation Fault Model for Timing-InducedFunctional Errors ... Amherst, MA 01003 qzhang@ecs.umass.edu, harris@ecs.umass.edu ... such as VHDL and Verilog, ...

Model, Timing, Fault, Errors, Verilog, Umass, Amherst, Fault model for timing, Fault model for timing inducedfunctional errors, Inducedfunctional

Siddharth Choudhuri Tony Givargis

www.ics.uci.eduSiddharth Choudhuri Tony Givargis Center for Embedded Computer Systems Center for Embedded Computer Systems University of California University of California Irvine, CA 92617, USA Irvine, CA 92617, USA e-mail: sid@cecs.uci.edu e-mail givargis@uci.edu Abstract— Software peripherals [1] have been proposed as a

Tony, Siddharth, Siddharth choudhuri tony givargis, Choudhuri, Givargis

The VHDL Golden Reference Guide - University of California ...

www.ics.uci.eduapplication to hardware design. The VHDL Golden Reference Guide is not intended as a replacement for the IEEE Standard VHDL Language Reference Manual. Unlike ... Circuit) Hardware Description Language. VHDL is a language for describing the behaviour and structure of electronic circuits, and is an IEEE standard (1076).

STATS8: Introduction to Biostatistics 24pt Probability

www.ics.uci.eduIntroduction We have used plots and summary statistics to learn about the distribution of variables and to investigate their relationships. We now want to generalize our ndings to the population.

Reducing Combinatorics in GUI Testing of Android Applications

www.ics.uci.eduAndroid, Software Testing, Input Generation 1. INTRODUCTION With well over a million apps, Android has become one of the dominant mobile platforms [16]. Android app markets, such as ... coverage as exhaustive combinatorial testing, but reduces the num-ber of test cases by 57.86% on average and by as much as 99.9%.

Learning Materials for Introductory Embedded Systems ...

www.ics.uci.eduLearning Materials for Introductory Embedded Systems Programming using a ModelBased Discipline Frank Vahid, Computer Science & Engin., Univ. of California, Riverside (also with zyBooks)

Programming, System, Material, Learning, Introductory, Embedded, Learning materials for introductory embedded systems, Learning materials for introductory embedded systems programming

Related documents

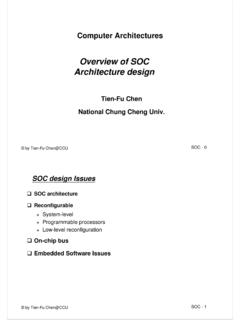

Overview of SOC Architecture design

www.cs.ccu.edu.twSystem Architecture Design System Architecture & Exploration What Hardware/Software partitioning; processor, and memory architecture choices; system timing budget, power management strategy, system verification strategy… Partitioning into HW block hierarchy, cycle time budgeting, block interfaces, block verification, clock architecture and ...

Intro to Verilog - MIT

web.mit.educhooses what architecture is used for a given instance of an entity. Design is composed of modules. Behavioral, dataflow and structural modeling. Synthesizable subset... Behavioral, dataflow and structural modeling. Synthesizable subset... Harder to learn and use, not technology-specific, DoD mandate Easy to learn and use, fast

Computer Architecture: Dataflow (Part I) - ECE:Course Page

course.ece.cmu.eduSome Required Dataflow Readings ! Dataflow at the ISA level " Dennis and Misunas, “A Preliminary Architecture for a Basic Data Flow Processor,” ISCA 1974. " Arvind and Nikhil, “Executing a Program on the MIT Tagged- Token Dataflow Architecture,” IEEE TC 1990. ! Restricted Dataflow

Architecture, Data, Flows, Flow data, Dataflow, Dataflow architecture

Modeling Latches and Flip-flops - Xilinx

www.xilinx.comCreate and add the VHDL module with the SR_latch_dataflow code. 1-1-3. Develop a testbench (see waveform above) to test and validate the design. 1-1-4. Add the appropriate board related master XDC file to the project and edit it to include the related pins, assigning S input to SW0, R input to SW1, Q to LED0, and Qbar to LED1. 1-1-5.

Business Blueprint STEP-BY-STEP guide

erpdb.infoAcceleratedSAP For more detailed information on data modeling and the BW Schema please refer to the Multi-Dimensional Modeling with BW Accelerator on SAP Service Market Place

Software architecture: Architectural Styles

www.win.tue.nl• Domain-Specific Software Architecture is a part of a Reference Architecture: FALSE • Domain-Specific Software Architecture is broader applicable than a product line: TRUE • Model-View-Controller is an examples of a Domain-Specific Software Architecture FALSE

18 447 Lecture 2: RISC V Instruction Set Architecture

users.ece.cmu.edu18‐447‐S21‐L02‐S1, James C. Hoe, CMU/ECE/CALCM, ©2021 18‐447 Lecture 2: RISC‐V Instruction Set Architecture James C. Hoe Department of ECE Carnegie Mellon University