Metastability

Found 7 free book(s)Clock and Synchronization

academic.csuohio.edu• Metastability is basically an “analog” phenomena • Metastability behavior is described by random variable • Metastability cannot be easily modeled or simulated in gate level (only ‘X’) • Metastability cannot be easily observed or measured in physical circuit (e.g., MTBF = 3 months) • MTBF is very sensitive to circuit revision

Clock Domain Crossing (CDC) Design & Verification ...

www.sunburst-design.comSep 26, 2008 · 2.0 Metastability Metastbility refers to signals that do not assume stable 0 or 1 states for some duration of time at some point during normal operation of a design. In a multi-clock design, metastability cannot be avoided but the detrimental effects of metastability can be neutralized. Figure 1 - Asynchronous clocks and synchronization failure

Lecture 8 - Timing Constraints

www.ee.ic.ac.ukMetastability is a problem that arises when an external input NOT synchronised to the system clock is fed into our synchronous circuit. Since the input signal could change anytime relative the the clock edge, metastability will occur. It could also happens when a signal crosses from one clock domain (Clock1) to another clock domain (Clock2).

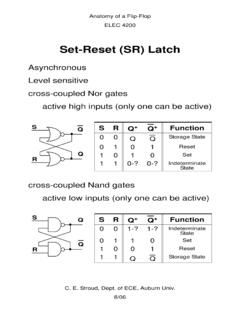

Set-Reset (SR) Latch

www.eng.auburn.eduAsynchronous interfaces lead to metastability (minimize the async interface & double clock data to reduce probability of metastability) Avoid asynchronous presets & clears on FFs (use sync presets & clears whenever possible) DO NOT construct a FF from two level sensitive latches of the same type with an inverter on the clock input to one latch

The Design of a Comparator [The Analog Mind]

www.seas.ucla.edumetastability analysis (as explained later). However, it is common in ADC design to select this difference to be half of the least-significant bit, which, in view of our tolerable off-set, would be 10–20 mV for this de-sign. However, we apply a difference of 1 mV so as to place the circuit in “slow motion” and examine its op-eration details.

Metastability - University of Southern California

www-classes.usc.eduMetastability in digital systems occurs when two asynchronous signals combine in such a way that their resulting output goes to an indeterminate state. A common example is the case of data violating the setup and hold specifications of a latch or a flip-flop. In an ideal

FIFO Intel® FPGA IP User Guide

www.intel.comFIFO Intel ® FPGA IP User Guide. Intel ® provides FIFO Intel FPGA IP core through the parameterizable single-clock FIFO (SCFIFO) and dual-clock FIFO (DCFIFO) functions.

![The Design of a Comparator [The Analog Mind]](/cache/preview/e/5/8/5/5/4/8/e/thumb-e585548ea77004de39ec628b8fd92b40.jpg)