Search results with tag "Serial peripheral interface"

Extending SPI and McBSP With Differential Interface Products

www.ti.comApplication Report SLLA142 - May 2003 1 Extending SPI and McBSP With DIfferential Interface Products Chris Sterzik HPL–Interface ABSTRACT The serial peripheral interface (SPI) and the multichannel buffered serial port (McBSP)

TMS320x2833x, 2823x DSC Serial Peripheral Interface (SPI

www.ti.comPreface SPRUEU3A–August 2008–Revised June 2009 This guide describes how the serial peripheral interface works. About This Manual The SPI module described in this reference guide is a Type 0 SPI.

SPI (Serial Peripheral Interface) NAND Flash Memory

www.endrich.comSPI (Serial Peripheral Interface) NAND Flash provides an ultra cost-effective while high density non-volatile memory storage solutionfor embedded systems, based on an industry-standard NAND Flash memory coreis an attractive. It alternative to SPI-NOR and standard parallel NAND Flash, with advanced features:

Quad-SPI interface on STM32 microcontrollers and ...

www.st.comApr 28, 2020 · The Quad-SPI is a serial interface that allows the communication on four data lines between a host (STM32) and an external Quad-SPI memory. The QUADSPI supports the traditional SPI (serial peripheral interface) as well as the Dual-SPI mode which allows to communicate on two lines. QUADSPI uses up to six lines in quad mode: one

AXI Quad SPI v3 - Xilinx

www.xilinx.comAXI Quad SPI v3.2 4 PG153 August 6, 2021 www.xilinx.com Product Specification Introduction The LogiCORE™ IP AXI Quad Serial Peripheral Interface (SPI) core connects the AXI4 interface to those SPI slave devices that support the Standard, Dual, or Quad SPI protocol instruction set. This core provides a serial interface to SPI slave devices. The

64/128 Mbit Single Operation Voltage - ISSI

www.issi.comIS37/38SML01G1 Integrated Silicon Solution, Inc.- www.issi.com 3 Rev. 0A 06/16/2017 GENERAL DESCRIPTION The serial electrical interface follows the industry-standard serial peripheral interface (SPI…

Low Noise, Low Drift, Low Power, 3-Axis MEMS ...

www.analog.comby their relevant function for either the serial peripheral interface (SPI) or limited I2C interface. 1 Protected by U.S. Patents 8,472,270; ... Changes to Serial Communications Section and Figure 64 ..... 26 Added SPI Bus Sharing Section and Figure 65; Renumbered ... Changes to Temperature Data Registers Section, Table 23, Table 24, and Table ...

ESP8266 Technical Reference - Espressif

www.espressif.com2016.06 V1.1 Added Section 4.5 Interface Description. 2016.08 V1.2 Updated Section 14.1 Sniffer Introduction. 2017.05 V1.3 Updated Section 4.1.2 SPI Features. 2019.08 V1.4 Updated Section 1.1 General Purpose Input/Output Interface (GPIO). 2020.07 V1.5 • Updated Section 1.3 Serial Peripheral Interface (SPI/ HSPI); • Added documentation feedback links. ...

Baruch Siach baruch@tkos.co - Haifux - Haifa Linux Club

www.haifux.orgWhat is Serial Peripheral Interface (SPI)? Synchronous serial digital data link by Motorola SPI master controls CLK: synchronization clock

PIC32 FRM - Section 23. Serial Peripheral Interface (SPI)

ww1.microchip.com23.1.3 Audio Protocol Interface Mode 23.1.3.1 SPI IN AUDIO MASTER MODE CONNECTED TO A CODEC SLAVE Figure 23-6 shows the Bit Clock (BCLK) and Left/Right Channel Clock (LRCK) as generated by the PIC32 SPI module. Figure 23-6: Master Generating its Own Clock – Output BCLK and LRCK 23.1.3.2 SPI IN AUDIO SLAVE MODE CONNECTED TO A CODEC MASTER

ENC28J60 Data Sheet - Microchip Technology

ww1.microchip.comOct 26, 2012 · with an industry standard Serial Peripheral Interface (SPI). It is designed to serve as an Ethernet network interface for any controller equipped with SPI. The ENC28J60 meets all of the IEEE 802.3 specifica-tions. It incorporates a number of packet filtering schemes to limit incoming packets. It also provides an

Enhanced methods to handle SPI communication on STM32 ...

www.st.comThe serial peripheral interface (SPI) permits transparent and easy handling of data transfer between peripheral and microcontroller. The SPI has a wide range of possible configurations, which increase the potential for trouble related to specific …

ATtiny202/204/402/404/406 - Microchip Technology

ww1.microchip.com– One host/client Serial Peripheral Interface (SPI) – One Two-Wire Interface (TWI) with dual address match • Philips I2C compatible • Standard mode (Sm, 100 kHz) • Fast mode (Fm, 400 kHz) • Fast mode plus (Fm+, 1 MHz) – One Analog Comparator (AC) with a low propagation delay – One 10-bit 115 ksps Analog-to-Digital Converter (ADC)

Preliminary Product Specification v1 - SparkFun Electronics

www.sparkfun.comYou can operate and configure the nRF24L01+ through a Serial Peripheral Interface (SPI). The register map, which is accessible through the SPI, contains all configuration registers in the nRF24L01+ and is accessible in all operation modes of the chip. The embedded baseband protocol engine (Enhanced ShockBurst™) is based on packet communication

AT25DF641A - Adesto Technologies

www.adestotech.com8793F–DFLASH–11/2017 Features Single 2.7V - 3.6V supply Serial Peripheral Interface (SPI) compatible Supports SPI Modes 0 and 3 Supports RapidS™ operation Supports Dual-Input Program and Dual-Output Read Very high operating frequencies 100MHz for RapidS 85MHz for SPI Clock-to-output time (tV) of 5ns maximum …

ENC28J60 Data Sheet - Microchip Technology

ww1.microchip.com2006-2012 Microchip Technology Inc. . DS39662E-page 3 ENC28J60 1.0 OVERVIEW The ENC28J60 is a stand-alone Ethernet controller with an industry standard Serial Peripheral Interface

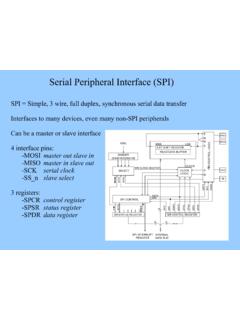

Serial Peripheral Interface (SPI) - Oregon State University

web.engr.oregonstate.eduSerial Peripheral Interface (SPI) Full duplex, synchronous serial data transfer Data is shifted out of the master's (mega128) MOSI pin and in it's MISO pin

Serial Peripheral Interface (SPI) with Audio Codec Support

ww1.microchip.com2013 Microchip Technology Inc. DS70005136A-page 5 Serial Peripheral Interface (SPI) with Audio Codec Support 1.2 Framed Mode SPI Operation In Framed mode operation, the frame master controls the generation of the Frame Synchroniza-

Serial Peripheral Interface (SPI) for KeyStone Devices ...

www.ti.comø-ii KeyStone Architecture Serial Peripheral Interface (SPI) User Guide SPRUGP2A—March 2012 www.ti.com Submit Documentation Feedback Release History

Similar queries

DIfferential, Serial Peripheral Interface, Serial Peripheral Interface SPI, Module, Serial, Xilinx, Interface, Section, Technical Reference, Baruch Siach, Section 23. Serial Peripheral Interface SPI, AUDIO, CODEC, ATtiny202/204/402/404/406, SparkFun Electronics, NRF24L01, Dual, ENC28J60 Data Sheet, MISO, Audio Codec, Architecture Serial Peripheral Interface SPI