Latches and Flip-Flops

edge triggered D-CE flip-flop of Figure 11-27(c). Assume Q begins at 1. a) First draw Q based on your understanding of the behavior of a D flip-flop with clock enable. b) Now draw the internal signal D from Figure 11-27(c), and confirm that this gives the same Q as in a).

Tags:

Edges, Triggered, Edge triggered

Information

Domain:

Source:

Link to this page:

Please notify us if you found a problem with this document:

Documents from same domain

Second Edition - 國立臺灣大學

www.csie.ntu.edu.twUSA Madison, WI 53706–1613 [email protected] USA [email protected] Series Editors: Thomas V. Mikosch University of Copenhagen Laboratory of Actuarial Mathematics DK-1017 Copenhagen ... A Method Based on Minimum-Change Updating ..... 228 9.3 Coordinate and Pattern-Search Methods . . . ..... 229 Coordinate Search Method ...

Introduction to Medical Image Processing

www.csie.ntu.edu.twuseful in many applications. The applications include detection of the coronary border in angiograms, multiple sclerosis lesion quantification, surgery simulations, surgical planning, measurement of tumor volume and its response to therapy, functional mapping, automated classification of blood cells, study of brain development,

Applications, Introduction, Medical, Image, Processing, Functional, Introduction to medical image processing

Orthogonal Frequency Division Modulation (OFDM)

www.csie.ntu.edu.twOrthogonal Frequency Division Multiplex (OFDM) Tutorial 1 Intuitive Guide to Principles of Communications www.complextoreal.com Orthogonal Frequency Division Multiplexing (OFDM) Modulation - a mapping of the information on changes in the carrier phase, frequency or amplitude or combination.

Division, Frequency, Modulation, Orthogonal, Ofdm, Orthogonal frequency division, Orthogonal frequency division modulation

Probability HW#5 - 國立臺灣大學

www.csie.ntu.edu.twThe lifetimes of interactive computer chips produced by a certain semicon-ductor manufacturer are normally distributed with parameters µ = 1.4×106 hours and σ = 3 × 105 hours. What is the approximate probability that a batch of 100 chips will contain at least 20 whose lifetimes are less than 1.8× 106. Solution.

Probability, Semicon, Semicon ductor, Ductor, Probability hw

A Comparison of Methods for Multi-class Support Vector ...

www.csie.ntu.edu.twThe voting approach described above is also called the “Max Wins” strategy. In case that two classes have identical votes, thought it may not be a good strategy, now we simply select the one with the smaller index. Practically we solve the dual …

Multi, Methods, Class, Support, Vector, Voting, Methods for multi class support vector

Path-loss and Shadowing (Large-scale Fading)

www.csie.ntu.edu.twMeasurements in Germany Cities Environment Path-loss Exponent Free-space 2 Urban area cellular radio 2.7-3.5 Shadowed urban cellular radio 3-5 Inbuilding LOS 1.6 to 1.8 Obstructed inbuilding 4 to 6 Obstructed in factories 2to 3

Reading: A Psycholinguistic Guessing Game

www.csie.ntu.edu.twReading: A Psycholinguistic Guessing Game Kenneth S. Goodman As scientific understanding develops in any field of study, preexisting, naive, common sense notions must give way. Such outmoded beliefs clut-ter the literature dealing with the process of reading.

Reading, Games, Psycholinguistic, Guessing, A psycholinguistic guessing game

ARM Instruction Set - 國立臺灣大學

www.csie.ntu.edu.tw• Instruction set defines the operations that can change the state. Memory system • Memory is a linear array of bytes addressed from 0 to 0x00000000 00 232-1 Wdf hl d bt 10 20 0x00000001 ... • See the reference manual (4 1 33)See the reference manual (4.1.33) Multiplication

Digital Logic Design - 國立臺灣大學

www.csie.ntu.edu.twIntroduction to Digital Logic Basics Hardware consists of a few simple building blocks ¾These are called logic gates AND, OR, NOT, … NAND, NOR, XOR, … L i t b ilt i t i tLogic gates are built using transistors NOT gate can be implemented by a single transistor AND gate requires 3 transistors Transistors are the fundamental devices Pentium consists of 3 million transistors

Computer Organization & Assembly Languages

www.csie.ntu.edu.twComputer Organization & Assembly Languages Pu-Jen Cheng Assembler Adapted from the slides prepared by Beck for the book, System Software: An Intro. to …

Related documents

Flip-Flops and Sequential Circuit Design

web.ece.ucsb.eduPositive edge triggered JK flip-flop. February 13, 2012 ECE 152A - Digital Design Principles 14 The Master Slave JK Flip-Flop

Mealy and Moore Machines - UC Santa Barbara

web.ece.ucsb.eduImplemented with falling edge triggered (by way of external inverter) JK flip-flops Schematic (following slide) J A = xB K A = x J B = x K B = xA z = xB’ + xA + x’A’B function of present state and present input

DM74LS74A Dual Positive-Edge-Triggered D Flip-Flops with ...

web.mit.eduDual Positive-Edge-Triggered D Flip-Flops with Preset, Clear and Complementary Outputs General Description This device contains two independent positive-edge-trig-gered D flip-flops with complementary outputs. The infor-mation on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering

Edges, Trig, Edger, Triggered, Edge triggered, Edge trig gered

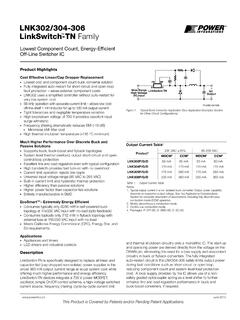

LNK302/304-306 LinkSwitch-TN Family - Power

www.power.comjitter should be measured with the oscilloscope triggered at the falling edge of the DRAIN waveform. The waveform in Figure 4 illustrates the frequency jitter of the LinkSwitch-TN. Feedback Input Circuit The feedback input circuit at the FEEDBACK pin consists of a low impedance source follower output set at 1.65 V. When the

Computer Architecture: Dataflow (Part I)

course.ece.cmu.eduBurger et al., “Scaling to the End of Silicon with EDGE Architectures,” IEEE Computer 2004. 8 . Data Flow ! ... Execution triggered by the presence of data ! Single assignment languages and functional programming " E.g., SISAL in Manchester Data Flow Computer " ...

Edge-triggered Flip-Flop, State Table, State Diagram

web.iit.edu• Edge-triggered: Read input only on edge of clock cycle (positive or negative) • Example below: Positive Edge-Triggered D Flip-Flop • On the positive edge (while the clock is going from 0 to 1), the input D is read, and almost immediately propagated to the output Q. Only the value of D at the positive edge matters. D C S C R D Clock Q Q

Online User’s Guide - Merrill Edge

www.merrilledge.com1 Merrill Edge MarketPro is available to clients who maintain a Merrill Edge self-directed relationship. To qualify, you must be a Platinum Privileges, Preferred Rewards Platinum or Preferred Rewards Platinum Honors client, or maintain total combined balances of $50,000 or more in your Merrill Edge investment accounts and Bank of America, N.A.

Immersive Experiences in Education

edudownloads.azureedge.netcognitive factors triggered by immersive technologies which are particularly relevant in a learning content. Embodied cognition Digitally immersive experience enable students to practice and perfect skills in a safe and accurate learning environment. Mastery-focused learning Evidence shows that test scores among students using Immersive Technology

Enhanced Serial Peripheral Interface (eSPI)

www.intel.comIntroduction 327432-004 9 2 Introduction This base specification describes the architecture details of the Enhanced Serial Peripheral Interface (eSPI) …