Transcription of Unclamped Inductive Switching Rugged MOSFETs For …

1 AN601 vishay SiliconixDocument Number: FaxBack 408-970-56001 Unclamped Inductive Switching Rugged MOSFETs For Rugged EnvironmentsThe evolution of the power MOSFET has resulted in a veryrugged transistor. The semiconductor industry defines thisruggedness as the capability to withstand avalanche currentswhen subjected to Unclamped Inductive Switching . Historically,MOSFET manufacturers chose to quantify ruggedness, notbased principally on individual performance, but rather oncomparative performance with other manufacturers. Siliconixhas optimized the cell structure of power MOSFETs , resultingin a new class of extremely Rugged devices.

2 Today savalanche-rated MOSPOWER FET exhibits a ruggednessthat far exceeds the performance of any power MOSFET ofearlier application note reviews the history of unclampedinductive Switching (UIS) and examines various theoriespertaining to failure. It further identifies what appears to be tworelated mechanisms thermal and bipolar believed to beresponsible for failure during Unclamped Inductive switchingand concludes by recommending how a power MOSFET should be qualified for ruggedness in the data failure modes exist when MOSFETs are subjected to this article, these failure mechanisms are labelled as eitheractive or passive.

3 The first, or active mode, results when theavalanche current forces the parasitic bipolar transistor intoconduction. The second, or passive mode, results when theinstantaneous chip temperature reaches a critical value.[1] Atthis elevated temperature, a mesoplasma * forms within theparasitic npn bipolar transistor and causes catastrophicthermal runaway. In either case, the MOSFET is passive mechanism is, therefore, identified as that failuremode not directly attributed to avalanche and DefinitionsWhenever possible, symbols and definitions established bythe JEDEC Committee, JC-25, are used in this article.

4 To clearup any discrepancies, however, the following list describessymbols used frequently in this peak current reached during avalanchetAVthe time duration of the avalanche phenomenonLthe value of inductanceV(BR)effthe breakdown voltage in avalancheWhat is Unclamped Inductive Switching ?Whenever current through an inductance is quickly turned off,the magnetic field induces a counter electromagnetic force(EMF) that can build up surprisingly high potentials across theswitch. Mechanical switches often have spark-suppressioncircuits to reduce these harmful effects that result when currentis suddenly interrupted.

5 However, when transistors are usedas the switches, the full buildup of this induced potential mayfar exceed the rated breakdown (V(BR)DSS) of the transistor,thus resulting in catastrophic we know the size of the inductor, the amount of current beingswitched, and the speed of the switch, the expected potentialmay be easily calculated asV =L di/dt + VDD(1)whereL =the inductance (H)di/dt=rate of change of current (A/s)VDD=the supply voltage (V)*A mesoplasma, according to Ghandhi, takes the form of a glowing red spot having an average temperature in excess of 650 C and a peak core temperature in excess of 1000 C.

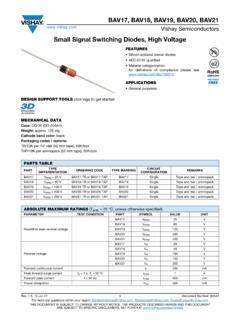

6 This mesoplasma is a result of regenerative thermal FaxBack 408-970-56002 Document Number: 7057215-Feb-94LI+ Test CircuitV(BR)effV(BR)DSSIOVDDtav0 FIGURE Waveform during SwitchingThe classic UIS test circuit in widespread use* is shown inFigure 1. Using this circuit, the energy absorbed by the powerMOSFET may be calculated using(2)E 1 2lo2L V(BR) effV(BR) eff VDD An alternate circuit removes VDD ( , VDD = 0) just prior toswitching the device off, thus eliminating the last term inequation (2).Reviewing the Switching waveform shown in Figure 2, thegate remains on long enough to ramp the current to IO, at whichtime the gate switches off, resulting in an abrupt break in thedrain current.

7 Since the magnetic field of the inductor cannotinstantaneously collapse, a voltage is induced on the drain ofthe MOSFET in accordance with equation (1). This inducedpotential may easily exceed the (avalanche) breakdownvoltage shown on the data sheet.** During avalanche, thevoltage is clamped at a value of V(BR)eff, and the current storedin the inductor decays linearly from IO to zero. This decay timemay be determined by rearranging equation (1).(3)tAV LloV(BR) effTheories Pertaining to Stress FailuresThe Bipolar Excitation Effect The Active Mode. Theclassic reason for failure when a MOSFET is stressed focuseson the activation and subsequent secondary breakdown of theparasitic bipolar transistor.

8 The intrinsic diode of a DMOS FETis actually the collector-base junction of this parasitictransistor. Whether the stress is a form of dv/dt[2,3] or UIS,current cascading laterally through the p+ region is consideredresponsible for transistor failure when the voltage drop, IORp+,activates this bipolar transistor.[4,5,6] The accepted modelrepresenting this failure mode in the vertical MOSFET structure is offered in Figure initial avalanche current at breakdown is heavilyconcentrated within the MOSFET s inherent Zener diode(afforded by the deep p+ well situated centrally in each cell, asshown in Figure 3).

9 However, as the avalanche currentcontinues to increase, it also spreads across the p/n lateral resistance (Rp) is much greater than the vertical resistance (RB) of the heavily-doped p+ region. Avalanchecurrent concentrated in the p+ (Zener) region does notnormally initiate bipolar action. As the avalanche currentincreases in intensity, it spreads along the p/n barrier, and thescenario follows the classic reasoning. If the avalanchecurrents cascading laterally through the p-doped region(pseudobase region) develop sufficient forward bias across Rpto offset VBE, the normal forward base current, +IB, inconjunction with the beta of the parasitic npn bipolar transistor,will result in a local breakdown voltage equal to BVCEO (whichis approximately half of V(BR)DSS).

10 The resulting mesoplasmacauses thermal runaway and the destruction of the powerMOSFET. *Recommended by JEDEC Committee JC 25.**Avalanche breakdown, V(BR)DSS, offered in the typical data sheet is generally rated at the zero gate voltage drain current (IDSS) of the MOSFET. Avalanche breakdown during UIS (V(BR)eff) is, as shown in Figure 2, at substantially higher drain currents. V(BR)eff is much greater than V(BR) SiliconixDocument Number: FaxBack 408-970-56003 DRAINGATESOURCERbDRAINGATESOURCERPn+RPRP RBPp+epi n IAIASUBSTRATE n+FIGURE Circuit and Cross SectionExamination of Figure 3 suggests that the current necessaryto trigger this series of events might be closely approximatedif both the VBE of the parasitic npn bipolar transistor and Rpwere known.