Arm Trace

Found 10 free book(s)A Primer: ARM Trace - SASE

www.sase.com.arETM: Embedded Trace Macrocell(ICE & CoreSight) Sends out PC and data reads and writes as fast as the core is. (E.ice) CoreSight only sends out all PC values. Use SWV for other data. PTM: Like ETM but for Cortex‐A9 and later. ETB: Embedded Trace Buffer (ICE & CoreSight)

UNITING AND STRENGTHENING AMERICA BY PROVIDING …

www.congress.govSec. 214. Pen register and trap and trace authority under FISA. Sec. 215. Access to records and other items under the Foreign Intelligence Surveil-lance Act. Sec. 216. Modification of authorities relating to use of pen registers and trap and trace devices. 18 USC 1 note. Uniting and Strengthening America by Providing Appropriate Tools Required ...

Intel® Arria® 10 Device Overview

www.intel.com• ARM CoreSight* JTAG debug access port, trace port, and on-chip trace storage External interfaces • Hard memory interface—Hard memory controller (2,400 Mbps DDR4, and 2,133 Mbps DDR3), Quad serial peripheral interface (QSPI) flash controller, NAND flash controller, direct memory access (DMA)

J-Link / J-Trace User Guide

www.segger.comChapter ”Working with J-Link and J-Trace“ *Section ”J-Link WiFi setup“ added 6.52 0 191021 AG Chapter ”Semihosting“ *Section ”Debugger Support“ Took off Keil MDK-ARM of the list of supported IDEs as MDK does not sup-port semihosting. 6.52 0 191016 LG Chapter ”RTT“ *Section ”Example code“ updated. 6.50 0 191016 LG

The Atmel-ICE Debugger - Microchip Technology

ww1.microchip.comARM ® Cortex®-M based ... • ITM serial trace capture at up to 3MB/s • Supports DGI SPI and USART interfaces when not debugging or programming • Supports 10-pin 50-mil JTAG connector with both AVR and Cortex pinouts. The standard probe cable supports AVR 6-pin ISP/PDI/TPI 100-mil headers as well as 10-pin 50-mil. An adapter is

Cortex-M0+ Devices Generic User Guide

www.keil.comThe ARM Glossary is a list of terms used in ARM documentation, together with definitions for those terms. ... Micro Trace Buffer (MTB) Optional Debug Access Port Cortex-M0+ Processor Optional Debug Cortex-M0+ Components Interrupts AHB-Lite interface to …

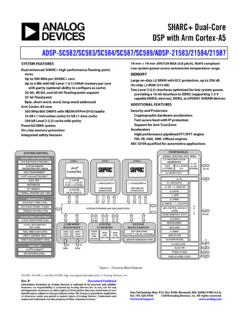

SHARC+ Dual-Core DSP with Arm Cortex-A5

www.analog.comArm Cortex-A5 (MHz, Max) 450 450 500 500 N/A N/A Arm Core L1 Cache (I, D kB) 32, 32 32, 32 32, 32 32, 32 N/A N/A Arm Core L2 Cache (kB) 256 256 256 256 N/A N/A SHARC+ Core1 (MHz, Max) 450 450 500 500 450 500 SHARC+ Core2 (MHz, Max) N/A 450 500 500 450 500 SHARC L1 SRAM (kB) 640 384 640 640 384 640 System Memory

Standing Orders for Administering Influenza Vaccine to Adults

www.immunize.orgFemale or male 130–152 lbs 22–25 1" Deltoid muscle of arm Female 153–200 lbs 22–25 1–1½" Deltoid muscle of arm Male 153–260 lbs 22–25 1–1½" Deltoid muscle of arm Female 200+ lbs 22–25 1½" Deltoid muscle of arm Male 260+ lbs 22–25 1½" Deltoid muscle of arm 4 Prepare to Administer Vaccine

ARM Cortex -A Series

www.macs.hw.ac.ukARM makes no representations or warranties, either express or implied, included but not limited to, warranties of merchantability, fitness for a particular purpose, or non-infringement, that the content of this Cortex-A Series Programmer’s Guide is suitable for any particular purpose or

LPC1769/68/67/66/65/64/63 Product data sheet - NXP

www.nxp.comThe Arm Cortex-M3 is a next generation core that offers system enhancements such as enhanced debug features and a higher level of support block integration. The LPC1768/67/66/65/64/63 operate at CPU frequencies of up to 100 MHz. The LPC1769 operates at CPU frequencies of up to 120 MHz. The Arm Cortex-M3 CPU