Junction Fet

Found 10 free book(s)Lecture 13: Amplifier Noise Calculations

rfic.eecs.berkeley.eduFET Layout To reduce the gate resistance, a multi-finger layout approach is commonly adopted. As a bonus, the junction capacitance is reduced due to the junction sharing. A. M. Niknejad University of California, Berkeley EECS 142 Lecture 13 p. 10/20 – p

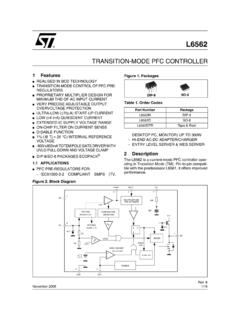

Transition-mode PFC controller - STMicroelectronics

www.st.comFET or IGBT drive which, combined with the other features, makes the device an excellent low-cost solu-tion for EN61000-3-2 compliant SMPS's up to 300W. ... Tj Junction Temperature Operating range -40 to 150 °C Tstg Storage Temperature -55 to …

BSS138 - N-Channel Logic Level Enhancement Mode Field ...

www.onsemi.comR JA is the sum of the junction−to−case and case−to−ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins. R JA is guaranteed by design while R JA is determined by the user’s board design. a) 350°C/W when mounted on a minimum pad. 2. Pulse Test: Pulse Width ≤ 300 s ...

ON Semiconductor Is Now

www.onsemi.comJunction Temperature Range TJ 125 °C Storage Temperature Range Tstg −65 to +150 °C Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are

How to Implement a MOSFET with a Gate Driver

www.egr.msu.eduNov 13, 2014 · Frequency, Junction. Introduction A MOSFET is an acronym for metal-oxide semiconductor field-effect transistor. It is a special type of field-effect transistor (FET) and is the key component in high frequency, high efficiency switching applications across the electronics industry. A MOSFET is a voltage controlled device.

SN74LVC1G3157 Single-Pole Double-Throw Analog Switch ...

www.ti.comTJ Junction temperature 150 °C Tstg Storage temperature –65 150 °C (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. 6.2 ESD Ratings VALUE UNIT V(ESD) Electrostatic discharge

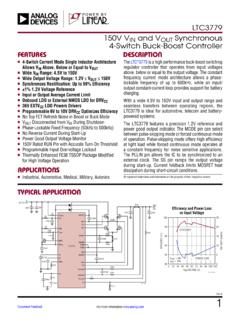

150V VIN and VOUT Synchronous 4-Switch Buck-Boost ...

www.analog.comLT 3779 4 For more information www.analog.com ELECTRICAL CHARACTERISTICS The l denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at TA = 25°C (Note 2), VIN = 15V, VRUN = 5V, VEXTVCC = 0V, VDRVSET = 0V, VVINOV = 0V unless otherwise noted. SYMBOL PARAMETER CONDITIONS …

Band-bending - Iowa State University

tuttle.merc.iastate.eduIn the p-n junction and BJT, we saw that the semiconductor band edges were bent in the depletion layers. We used the depletion approximation and Poisson’s equation to relate the band-bending (barrier height) to the electric field to the depletion layer width. In the case of depletion, our treatment is reasonably accurate. However, we

EPC2019 – Enhancement Mode Power Transistor

epc-co.comeGaN® FET DATASHEET EPC2019 EPC – POWER CONVERSION TECHNOLOGY LEADER | EPC-CO.COM | ©2022 | | 4 Figure 12: Transient Thermal Response Curves Junction-to-Board t1, Rectangular Pulse Duration, seconds Duty Cycle: Notes: Duty Factor: D = t 1/t 2 Peak T J = P DM x Z θJB x R θJB + T B P DM t 1 t 2 0.5 0.1 0.05 0.02 0.01 Z Single Pulse θJB

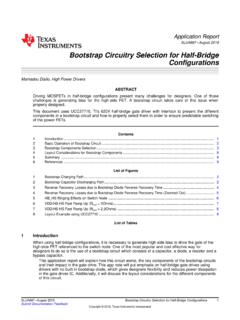

Bootstrap Circuitry Selection for Half Bridge Configurations

www.ti.comA bootstrap circuit is used in half-bridge configurations to supply bias to the high-side FET. Figure 1 shows the charging path of a bootstrap circuit in a simplified half-bridge configuration using UCC27710, TI's 620V half-bridge driver with interlock. When the low-side FET is on (high-side FET is off), the HS pin and the