Logic Cells

Found 11 free book(s)FPGA Logic Cells Comparison - Sharif

ee.sharif.eduFPGA Logic Cells Comparison In this article we compare logic cells architectures that are used in modern FPGAs: Xilinx (both Virtex-5 and earlier), Altera and Actel. Introduction FPGA (Field Programmable Gate Array) is an integrated circuit containing a matrix of user-programmable logic cells, being able to implement complex digital circuitry.

Chapter 4: Programmable Logic Devices 4.1 Chapter …

www.csun.eduLogic Devices include simple as well as high-density PLDs. In 1985 Xilinx Corporation came out with the first FPGA. It introduced the Logic Cell Array (LCA) and was the building block for all FPGAs to follow. It contained a pool of independent logic cells and multiple routing resources that allowed any logic cell

© Copyright 2015 2021 Xilinx

www.xilinx.comSystem Logic Cells (K) 96 170 238 308 CLB Flip-Flops (K) 88 156 218 282 CLB LUTs (K) 44 78 109 141 Max. Dist. RAM (Mb) 1.0 2.5 3.2 4.7 Total Block RAM (Mb) 3.5 5.1 7.0 10.5 36K Block RAM Blocks 100 144 200 300 UltraRAM (Mb) – – – – Clock Management Tiles (CMTs) 3 3 3 4 DSP Slices 400 576 900 1,200

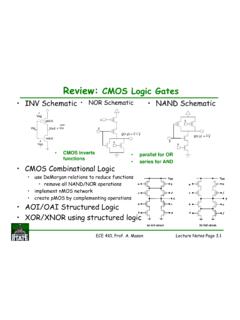

Review: CMOS Logic Gates - Michigan State University

www.egr.msu.eduReview: CMOS Logic Gates • NOR Schematic x x y g(x,y) = x y x x y ... – consider how signals will be routed in/out of the cells • don’t block access to I/O signals with substrate/well contacts no i taz imi n Miae ArD•S/ – minimize S/D junction areas to keep capacitance low

Adafruit PCA9685 16-Channel Servo Driver

cdn-learn.adafruit.comNov 15, 2021 · VCC - This is the logic power pin, connect this to the logic level you want to use for the PCA9685 output, should be 3 - 5V max! It's also used for the 10K pullups ... NiMH rechargeable cells. 4.8 or 6v Rechargeable RC battery packs from a hobby store. Adding a Capacitor to the thru-hole capacitor slot

Memory Testing and Built -In Self -Test - Elsevier.com

booksite.elsevier.comA coupling fault (CF) between two cells occurs when the logic value of a cell is influenced by the content of, or operation on, another cell. State Coupling Fault (CFst) – Coupled (victim) cell is forced to 0 or 1 if coupling (aggressor) cell is in given state. Inversion Coupling Fault (CFin)

Carry Lookahead Adder (CLA) - LSU

www.ece.lsu.educla5 Carry Generation Logic cla5 Lookahead CGL for first three cells. a0 b0 CLC0 p0 g0 s0 c0 CLC a1 b1 CLC1 p1 g1 s1 c1 CLC A B carry in S a2 b2 CLC2 p2 g2 s2 c2 CLC a3 b3 CLC3 p3 g3 s3 c3 CLC g-1 cla5 LSU EE 3755 Lecture Transparency. Formatted 8:33, …

LOGIC DESIGN LABORATORY MANUAL - ElectricVLab

electricvlab.comEach logic family has its own basic electronic circuit upon which more complex digital circuits and functions are developed. The following logic families are the most frequently used. ... The cells are arranged in such a way that any two immediately adjacent cells correspond to two minterms of distance 1. There is more than one way to construct ...

Computer Systems Design and Architecture

people.cs.clemson.edu• Digital logic level: gates, memory elements, buses • Electronic design level • Semiconductor physics level • Interactions and relations between levels • View of machine at each level • Tasks and tools at each level • Historical perspective • Trends and research activities This course

WebAIM's WCAG 2 Checklist

webaim.orgare used for tabular data and data cells are associated with their headers. Data table captions, if present, are associated to data tables. Text labels are associated with form input elements. Related form elements are grouped with fieldset/legend. ARIA labelling may be used when standard HTML is insufficient. 1.3.2 Meaningful Sequence (Level A ...

Toulmin Model of Argument - C-N

web.cn.eduIV. Offer factual backing to show that logic used in the warrants is good in term of realism as well as theory. A. Backing for Warrant #1 B. Backing for Warrant #2 C. (and so on) V. Discuss counter-arguments and provide rebuttal A. Counter-argument #1 B. Rebuttal to counter-argument #1 C. Counter-argument #2 D. Rebuttal to counter-argument #2