Transcription of The Fujitsu 56GSa/s Analog-to-Digital Converter Enables ...

1 The Fujitsu 56 GSa/s Analog-to-Digital Converter Enables 100 GbE transport Ultra-fast CMOS ADC Provides Technology Breakthrough for Upcoming Telecommunication Applications Te chn ol ogy Backgrounder The Fujitsu 56 GSa/s Analog-to-Digital Converter Enables 100 GbE transport Introduction to Analog-to-Digital needs to be no more than a few watts each to fit within Converter for 100 Gbps Systems the power constraints imposed by the system. Until recently it was thought that technology such as very A 100 Gbps coherent receiver needs four 56 GSa/s advanced SiGe or ultra-small-geometry CMOS (40nm Analog-to-Digital Converters (ADCs) and a tera-OPS or smaller) would be needed to meet these DSP that dissipates only tens of watts.

2 This paper requirements and still have the sufficient dynamic range discusses the forces pushing towards a single-chip for input signals up to 15 GHz and higher. By CMOS solution. The paper also introduces the Fujitsu extrapolating from historic advances in ADC design it ultra-fast CMOS ADC, which provides the enabling was predicted at the end of 2008 that suitable ADCs technology for 100 Gbps Ethernet and OTU-4 transport would not be available until 20131. systems using coherent receivers. However, the development of new circuit techniques To provide a long-haul 100 Gbps optical transport means that these ADCs actually became available in network with maximum reach and immunity to optical 2009 using 65nm CMOS2.

3 This accelerated the date by fiber non-idealities, the industry has settled on dual- when single-chip 100 Gbps coherent receivers became polarization, quadrature, phase-shift keying (DP-QPSK) technically and economically feasible, and significantly as a modulation method. This means that a coherent changed the industry roadmap for these devices. receiver is required. The biggest implementation challenge resulting from this decision is the need for In addition to covering the technical issues described low-power, ultra-high-speed ADCs. Their technology above, this paper discusses Fujitsu 's first customer requirements define the way such a receiver can be evaluation silicon (ROBIN) for the CHArge-mode implemented.

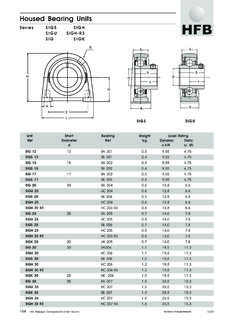

4 Interleaved Sampling (CHAIS) technology containing a two-channel 56 GSa/s version of the ADC. Without suitable ADCs especially without those with low enough power consumption it is impossible to The Drive Towards a Single-Chip CMOS. produce a 100 Gbps coherent receiver that is useful for a commercial optical network (as opposed to a ADC DSP. prototype system suitable only for demonstration in the A DP-QPSK coherent receiver needs four ADC. lab). Also, in the future such ADCs will be required for channels (Figure 1) since there are two optical higher-speed short-haul links, where low power and polarizations. Each channel needs two ADCs to digitize cost become even more important because there are an I/Q signal.

5 To achieve a 100 Gbps net line rate, a many more short-haul links than long-haul ones. baud rate of at least 28 Gbaud/s is used to allow for overhead, which needs 56 GSa/s ADCs. The system These ADCs need sampling rates of at least 56 GSa/s SNR requirements mean that 6-bit resolution or higher and resolution of 6 bits or more. Power consumption 100G MUX. Electrical SFI-S / MLD / XFI. 10 to 4 MUX. SFI-S. SFI-S. Precoding Optical To network 10 * Gbps 4 * 28 Gbps To system OTU-4. OTU-4 112 Gbps (Router). Framer / FEC. 100G client module for * 100G Ethernet or ADC. Optical SFI-S / MLD / XFI. * OTU-4. ADC. SFI-S. SFI-S. DSP. Electrical ADC. ADC. 100G Coherent Receiver ADC + DSP. Optical Module Figure 1 100 Gbps Coherent Optical Transponder Page 1 Fujitsu Microelectronics America, Inc.

6 The Fujitsu 56 GSa/s Analog-to-Digital Converter Enables 100 GbE transport is typically required to allow some margin for added demultiplexing front-end and clock circuits, as well as noise and distortion. So, for four ADCs, the output data the back-end ADC power. rate to the DSP is or if 8-bit resolution is used to allow more margin and/or digital AGC after To achieve such high speed and resolution, multiple the ADC. lower-rate interleaved ADCs are used, driven by one or more wideband sample-and-hold (S/H) circuits, usually If the ADCs are not integrated with the DSP, this huge with more demultiplexing in between. The S/H circuits amount of data has to be transmitted between the need very wide bandwidth and low distortion, which is chips, which is not only difficult to implement (a very why either SiGe or very small geometry CMOS (40nm large number of channels with a high data rate), but or smaller) is normally said to be needed for 56 GSa/s.

7 Uses a lot of power for serialization, de-serialization and However, with the sub-1V supply voltages imposed by transmission. Even using an optimistic figure of 40nm CMOS, it is difficult to design an S/H with 100mW/ch for an 11 Gbps channel (ADC transmit + reasonably large signal swing (to preserve SNR) and DSP receive), this means 3-4W per ADC is needed just linearity (to preserve THD). Higher-voltage SiGe avoids to transfer the data. This is acceptable for a prototype or these problems, but dissipates much more power. demonstrator, but not for a production solution. The small device sizes available in modern CMOS. A 100 Gbps receiver DSP which performs functions processes combine low power consumption and high such as equalization, chromatic dispersion density with high speed, but this comes at the price of compensation, and data recovery needs on the order increased noise and mismatch.

8 The normal solution to of 50M gates. This mandates the use of CMOS. The this is to increase transistor sizes (gate length and/or system power requirement for a complete coherent width), but this is not possible here because it is not receiver is only a few tens of watts. Since a 40G feasible to reduce bandwidth or increase power ADCDSP chip in 90nm already dissipates more than consumption. Small transistors mean poor matching in 20W3, geometries of 65nm or smaller, as well as power- both S/H and ADC, not just in the signal paths but also efficient design techniques, are needed for a 100G in the clock paths, where 100fs clock skew causes - receiver. 40dBc distortion for a 16 GHz input signal. The only feasible way to reduce these mismatch-induced errors This implies that the ADC should also use CMOS, is by widespread on-chip calibration.

9 Though this makes the design extremely challenging. A. single-chip solution is really the only viable way forward, Providing clock-skew adjustment is not so difficult in especially to take advantage of future CMOS theory. Measuring and calibrating skew down to sub- technology improvements. However, this assumes that pico-second accuracy is a much bigger problem, the ADC performance scales similarly to digital circuits, especially maintaining this accuracy over time and which may not be true for conventional ADCs. Even if a environmental variations without taking the ADC off-line multi-chip solution could be built ( , using SiGe for calibration or needing a large amount of complex ADCs together with a CMOS DSP in a multi-chip data analysis to calculate the errors.)

10 Module), the overall power would be higher, the production cost greater and the yield of such a complex CHArge-mode Interleaved Sampling solution inevitably lower. This approach also does not (CHAIS) ADC. provide a good roadmap towards even lower-power and cost-effective solutions for short-haul and beyond One way to overcome these challenges is to use a new 100 Gbps. sampler/demultiplexer architecture2 which gives the linearity, noise and bandwidth required without needing 56 GSa/s CMOS ADC Challenges extremely short-channel (40nm or below) transistors. The new architecture also allows simple calibration of Designing a 56 GSa/s 6-8b ADC in any technology amplitude and timing errors during operation and presents major difficulties.