Search results with tag "Iimp"

FMC 双目 MIPI 摄像头 采集模块

www.alinx.vip因为fpga 的接口没有直接支持mipi d-phy 的电平标准,所以需要一个桥 接芯 mc20901 进行电平的转换。mc20901 为5 通道的mipi d-phy 电路转 换芯,摄像头输出的 4 路lane 数据和1 路时钟lane 的mipi 信号通过 mc20901 芯转换成 fpga 芯支持的 lvds 差分信号。下图为mc20901 第

Patentes y Modelos de Utilidad - gob.mx

www.gob.mx3 Patentes y Modelos de Utilidad GUÍA DEL USUARIO De acuerdo con la Ley de la Propiedad Industrial (LPI), el Instituto Mexicano de la Propiedad Industrial (IMPI) tiene, entre otras atribuciones, fomentar y proteger

Understanding and Performing MIPI D-PHY Physical Layer ...

download.tek.comUnderstanding and Performing MIPI® D-PHY Physical Layer, CSI and DSI Protocol Layer Testing Application Note Introduction Currently many technologies are used in designing mobile or portable devices. These current interfaces are not well defined and are proprietary for each component or subsystem vendor.

Layout Design Guide - Toradex

docs.toradex.comapplication was the Flat Panel Display Link, LVDS became a synonymous for this interface. In this document, the term LVDS is used for the FPD-Link interface. MIPI Mobile Industry Processor Interface Alliance MDI Medium Dependent Interface, physical interface between Ethernet PHY and cable connector

MIPI Alliance Overview - ti.com

www.ti.commipi スタンダードの意義 部品サプライヤにとって 携帯端末メーカー プロセッサ-ペリフェラルデバイス間の物理的 インターフェースについての業界におけるより

PGY-HSI Datasheet MIPI-HSI Electrical Validation …

www.prodigytechno.comPGY-HSI Datasheet MIPI-HSI Electrical Validation and Protocol Decode Software Detail View correlates Waveform, Protocol and electrical measurements

MIPI Display Interface Controller - Solomon Systech

www.solomon-systech.comPioneering in MIPI solutions for display, Solomon Systech is proud to present a series of proprietary MIPI Bridge Chips that support high-resolution, high-speed and low-power display of

SN65DSI83 MIPI DSI Bridge to FLAT LINK LVDS …

www.ti.comProduct Folder Sample & Buy Technical Documents Tools & Software Support & Community SN65DSI83 SLLSEC1G –SEPTEMBER 2012–REVISED JUNE 2015 SN65DSI83 MIPI® DSI Bridge to FlatLink™ LVDS

MIPI CSI-2 Receiver Subsystem v3 - Xilinx

www.xilinx.comMIPI CSI-2 Receiver Subsystem v3.0 LogiCORE IP Product Guide Vivado Design Suite PG232 April 4, 2018

Raspberry Pi 4 Computer

static.raspberrypi.org2-lane MIPI DSI display port 2-lane MIPI CSI camera port 4-pole stereo audio and composite video port Multimedia: H.265 (4Kp60 decode); H.264 (1080p60 decode, 1080p30 encode); OpenGL ES, 3.0 graphics SD card support: Micro SD card slot for loading operating system and data storage Input power: 5V DC via USB-C connector (minimum 3A1)

SN65DSIx6-Q1 MIPI® DSI to eDP™ Bridge - TI.com

www.ti.comSN65DSI86-Q1 www.ti.com SLLSEJ5A –JULY 2014–REVISED DECEMBER 2015 Pin Functions (continued) PIN TYPE DESCRIPTION NAME NO. DB3P 12 I MIPI D-PHY Channel B Data Lane 3; data rate up to 1.5 Gbps.

M31 MIPI CDPHY M31708 p

www.m31tech.comThe IP boutique like the M31 galaxy, inspiring unlimited imagination and bringing us a brighter future Block Diagram MIPI C/D-PHY Combo TX BIAS

SN65DSI86 MIPI® DSI to eDP™ Bridge - Texas …

www.ti.comwww.ti.com. . .. . .

Display Interface Controller IC - Solomon Systech

www.solomon-systech.comFeatures. SSD2861 • Support 24bit video mode of up to 2560 x 1800 • Support input of eDP at 1.62Gbps or 2.7Gbps/lane for 4 lanes • Support output of MIPI-DSI at 1.0Gbps/lane for 8 lanes

MIPI D-PHY Interface Test

www.koreatest.or.krMIPI D-PHY IP Core Overview MIPI D-PHY is a High-speed low power serial transceiver interface supporting interconnections of a wide range of low-power high-speed mobile applications such as digital

キュリアス株式会社 - curious-jp.com

www.curious-jp.comASIPとは? Application SpecificIPの略で特定用途向けIP (カスタムIP)を示す。弊社の造語。 Rev.2.70 3 専門用語の説明 キュリアスIPデータベース SLVS-EC MIPI-DPHY / MPHY

MT9M114 - 1/6‐inch 720p High‐Definition (HD) …

www.onsemi.comMT9M114 www.onsemi.com 4 1. This typical configuration shows only one scenario out of multiple possible variations for this sensor. 2. If a MIPI Interface is not required, the following signals must be left floating: DATA_P, DATA_N, CLK_P, and CLK_N.

i.MX 6Dual/6Quad Applications Processor Data Sheet for ...

www.nxp.com† Interface flexibility—Each processor supports connections to a variety of interfaces: LCD controller for up to four displays (including parallel display, HDMI1.4, MIPI display, and LVDS display), dual CMOS sensor in terface (parallel or through MIPI ), …

Raspberry Pi 4 Computer Model B

static.raspberrypi.org2-lane MIPI DSI display port 2-lane MIPI CSI camera port 4-pole stereo audio and composite video port Multimedia: H.265 (4Kp60 decode); H.264 (1080p60 decode, 1080p30 encode); OpenGL ES, 3.0 graphics SD card support: Micro SD card slot for loading operating system and data storage Input power: 5V DC via USB-C connector (minimum 3A1)

i.MX 8 Series and Layerscape Processor Comparison Table - NXP

www.nxp.comDisplay Interface 2 x MIPI-DSI (4-lanes each), 2 x LVDS, 1 x HDMI 2.0a/eDP 1.4/DP 1.3 with HDCP 2.2; Dual display processor with SafeAssure® certification 2 x MIPI-DSI/LVDS (4-lanes each) or 1 x 8-lane LVDS with combo PHY; 1 x parallel LCD (24-bit RGB); Display processor with SafeAssure certification

i.MX 8 FAMILY OF APPLICATIONS PROCESSORS

www.nxp.com1 x MIPI DSI (4-lanes) 1 x MIPI CSI (4-lanes) 1 x MIPI CSI 1 x LVDS Tx 1 x HDMI 2.0a/eDP 1.4/DP 1.3 with HDCP 2.2 1 x HDMI 1.4 Rx with HDCP 2.2 1 x LVDS Tx 1 x MIPI DSI (4-lanes) Video: h.265 dec 4K/2K h.264 dec/enc 1080p 1 x 4-8 …

MIPI/DSI Receiver with HDMI Transmitter Data Sheet ADV7533

www.analog.comMIPI/DSI receiver 2-, 3-, or 4-lane DSI receiver Supports up to 800 Mbps per lane Compatible with DPHY V.0.90 and DSI V.1.02 Supports inputs of 16-bit RGB 4:4:4 24-bit RGB 4:4:4 30-bit RGB 4:4:4 HDMI (TMDS) video out 80 MHz operation supports all video and graphics resolutions from 480i to 1080p at 30 Hz Programmable 2-way color space converter

Raspberry Pi 3 Model B+

datasheets.raspberrypi.comMIPI DSI display port MIPI CSI camera port 4 pole stereo output and composite video port H.264, MPEG-4 decode (1080p30); H.264 encode (1080p30); OpenGL ES 1.1, 2.0 graphics Micro SD format for loading operating system and data storage 5V/2.5A DC via micro USB connector 5V DC via GPIO header Power over Ethernet (PoE)–enabled (requires separate ...

Intel CES 2022

download.intel.comMIPI CSI (IPU) 50x25x1.3mm BGA package eDP 1.4b HBR3 x8 PCIe Gen4 SPI/eSPI GbE LAN LP4x, LP5 DDR4, DDR5 4x TBT4 2x4 PCIe Gen4 10x USB2 4x USB3 x12 PCIe Gen3 ... ≥14” Display ≥16mm ~35W SoC. Performance On The Go. ≥15” Display ≥18mm ~45W SoC. Amazing Performance in sleek form factor. ≥15” Display ≥20mm ~65W So

MIPI Alliance Specification for D-PHY

www.jmrcubed.comD-PHY specification v0.65 or D-PHY specification v0.90 which are superseded by this version (v1.00.00). It is the good faith expectation of the MIPI PHY WG that there will be no significant functional changes to the fundamental technology described in this specification.

F133 - whycan.com

whycan.com- RGB interface up to 1920 x 1080@60fps - Dual link LVDS interface up to 1920 x 1080@60fps - 4-lane MIPI DSI up to 1920 x 1200@60fps - CVBS OUT interface, supporting NTSC and PAL format Video Input - 8-bit digital camera interface - CVBS IN interface, supporting NTSC and PAL format (only for F133-B) Analog Audio Codec

Infiniium S 系列高清示波器 - Keysight

www.keysight.comJul 16, 2019 · d9010mplp mipi rffe i3c spmi d9010mcdp mipi csi/dsi c-phy [2] d-phy d9010mpmp mipi m-phy digrf lli csi-3 unipro ufs ssic d9010milp arinc 429 mil-std 1553 spacewire d9010bdlp [1] sent 100base-t1 spacewire spi [3] 1. d9010bdlp

STM32MP1 Series interfacing with a MIPI® CSI-2 camera ...

www.st.comThe MIPI CSI-2.1 interface can theoretically achieve data throughput rates up to 2.5 Gbyte/s per lane with a D-PHY . This is hardly achievable on a parallel port interface due firstly to I/O slew rate pin constraints on a general-purpose device such as the STM32MP1 Series, which only have a MIPI CPI interface. ...

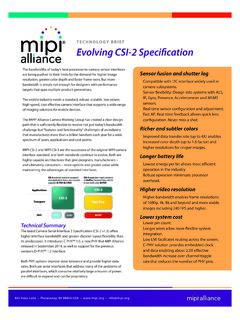

Evolving CSI-2 Speci˜ cation - MIPI Alliance

www.mipi.orgThe table below illustrates optimal MIPI CSI and PHY con˝ gurations for popular 4K imaging format: TECHNOLOGY BRIEF Evolving CSI-2 Speci˜ cation CSI-2 over D-PHY and C-PHY D-PHY as used in CSI-2 is a unidirectional di˜ erential interface with one 2-wire forwarded clock lane and one or more 2-wire

DATA SHEET [PRELIMINARY] NVIDIA Jetson Xavier NX …

www.miivii.com10/100/1000 Gigabit Ethernet | Media Access Controller (MAC) Imaging 12 lanes (3 x4 or 6 x2 or 6 x1) MIPI CSI-2 | D-PHY 1.2 (2.5 Gb/s per pair, total up to 30 Gbps) Display Controller Two multi-mode (eDP/DP/HDMI) Serial Output Resources (SOR) eDP 1.4a | DP 1.4 | HDMI 2.0a/b Maximum Resolution (eDP/DP/HDMI): (up to) 3840x2160 at 60 Hz

Camera Serial Interface - MIPI Alliance

www.mipi.orgMIPI, MIPI Alliance and the dotted rainbow arch and all related trademarks, tradenames, and other intellectual property are the exclusive property of MIPI Alliance and cannot be used without its express prior written

MIPI Alliance Specification for Camera Serial Interface 2 ...

caxapa.ruCamera Serial Interface 2 (CSI-2) Draft Version 1.01.00 Revision 0.04 – 2 April 2009 Further technical changes to this document are expected as work continues in the Camera Working Group . Version 1.01.00 r0.04 2-Apr-2009 DRAFT MIPI Alliance Specification for CSI-2

STM32L4R5xx STM32L4R7xx STM32L4R9xx

www.st.com–MIPI® DSI Host controller with two DSI lanes running at up to 500 Mbits/s each – LCD-TFT controller • 16x timers: 2 x 16-bit advanced motor-control, 2 x 32-bit and 5 x 16-bit general purpose, 2x 16-bit basic, 2x low-power 16-bit timers (available in Stop mode), 2x watchdogs, SysTick timer • Up to 136 fast I/Os, most 5 V-tolerant, up to 14

MIPI–CSI2 Peripheral on i.MX6 MPUs

www.nxp.comMIPI–CSI2 Peripheral on i.MX6 MPUs, Application Note, Rev. 0, 07/2016 2 NXP Semiconductors 1.3. Audience This document is intended for those who: • Need more information about the MIPI-CSI2 peripheral and its usage. • Need to implement or debug a driver to capture still or moving images by the i.MX6 family

i.MX RT1170 Crossover Processors Data Sheet for ... - NXP

www.nxp.com— MIPI Display Serial Interface (MIPI DSI) – PHY integrated – 2 data lanes interface with up to 1.5 GHz bit rate clock — Smart LCD Display with 8080 interface through SEMC • Audio: i.MX RT1170 Crossover Processors Data Sheet for Consumer Products, Rev. 2, 11/2021

CV22 - Computer Vision SoC for Consumer Cameras

www.ambarella.comMIPI DSI / CSI-2 GIGABIT ETHERNET ANALOG VIDEO OUT IDC SDIO SDXC SENSOR 2 ADC CV INTERNAL MEMORY HDMI / PARALLEL VIDEO INPUT / SENSOR . Drone • Person detection and tracking • Object detection / classification (CNN-based) Intelligent Video Analytics • vision processor for CNN / DNN edge analytics

Raspberry Pi Compute Module 4

datasheets.raspberrypi.com•MIPI DSI: 1 × 2-lane MIPI DSI display port 1 × 4-lane MIPI DSI display port •MIPI CSI-2: 1 × 2-lane MIPI CSI camera port 1 × 4-lane MIPI CSI camera port •1 × SDIO 2.0 (CM4Lite) •Single +5v PSU input. Raspberry Pi Compute Module 4 1.2. Features 4

株式会社ネットビジョン - net-vision.co.jp

www.net-vision.co.jphttp://www.net-vision.co.jp/ 1 Jul 06 2018 Smart Vision series 株式会社ネットビジョン Camera inspection Parallel-IF MIPI-IF Jig SerDes FPDLinkⅢ GMSL GVIF ...

Similar queries

MIPI, MIPI D, De la Propiedad Industrial, Instituto Mexicano de la Propiedad Industrial IMPI, CSI and DSI Protocol Layer Testing, Layout, Display, MIPI Mobile Industry Processor Interface, MIPI Alliance Overview - ti.com, Datasheet MIPI-HSI Electrical Validation, Datasheet MIPI-HSI Electrical Validation and Protocol Decode, MIPI Display Interface Controller, Solomon Systech, SN65DSI83 MIPI DSI Bridge to FLAT LINK LVDS, SN65DSI83, SN65DSI83 MIPI® DSI Bridge to, MIPI CSI-2 Receiver Subsystem, Xilinx, MIPI DSI, Texas, Display Interface Controller IC, Lanes, Interface, Controller, MIPI Display, In terface, Camera, MIPI/DSI, MIPI Alliance Specification, Specification, Series interfacing with a MIPI® CSI, MIPI CSI, DATA SHEET [PRELIMINARY] NVIDIA Jetson Xavier NX, Display Controller, MIPI Alliance, MIPI Alliance Specification for Camera Serial Interface, Serial Interface, MIPI® DSI, MIPI–CSI2 Peripheral on i.MX6, Application, Family, Raspberry Pi, Parallel

![DATA SHEET [PRELIMINARY] NVIDIA Jetson Xavier NX …](/cache/preview/c/b/1/9/2/4/a/0/thumb-cb1924a0bc504e526ece10c38e4b6630.jpg)