C programming for embedded system applications

PORTA = c | 0x01; // write c to PORTA with bit 0 set to 1 Fall 2014 - ARM Version ELEC 3040/3050 Embedded Systems Lab (V. P. Nelson) Example of µC register address definitions in

Download C programming for embedded system applications

Information

Domain:

Source:

Link to this page:

Please notify us if you found a problem with this document:

Documents from same domain

FUNDAMENTALS OF ENGINEERING (FE) …

www.eng.auburn.eduFUNDAMENTALS OF ENGINEERING (FE) EXAMINATION REVIEW www.railway-technology.com ELECTRICAL ENGINEERING Charles A. Gross, Professor Emeritus Electrical and Comp Engineering

Engineering, Examination, Fundamentals, Fundamentals of engineering

ELEC 2210 - EXPERIMENT 1 Basic Digital Logic Circuits

www.eng.auburn.eduELEC 2210 - EXPERIMENT 1 Basic Digital Logic ... • Develop professional lab skills and ... More details can be found in most textbooks on digital electronics, ...

Basics, Electronic, 2012, Digital, Experiment, Logic, Digital electronics, 2210 experiment 1 basic digital logic

C programming for embedded system applications

www.eng.auburn.eduassembly language programming. V. P. Nelson Fall 2014 - ARM Version ELEC 3040/3050 Embedded Systems Lab ... C programming for embedded system …

DC-DC Power Converters - Auburn University

www.eng.auburn.eduArticle in Wiley Encyclopedia of Electrical and Electronics Engineering DC-DC Power Converters Robert W. Erickson Department of Electrical and Computer Engineering

VHDL OPERATORS - Auburn University

www.eng.auburn.eduVHDL OPERATORS C. E. Stroud, ECE Dept., Auburn Univ. 1 8/06 Logic operators are the heart of logic equations and conditional statements AND OR …

A Gray-Code Current Mode ADC Structure

www.eng.auburn.eduA Gray-Code Current Mode ADC Structure ... the operating range and precision of the overall circuit. ... absolute value circuits used in this work are by no means the

Code, Dome, Current, Value, Structure, Precision, Absolute, Circuit, Absolute value circuits, Code current mode adc structure

VHDL 2 – Combinational Logic Circuits

www.eng.auburn.edu(Processes will be covered in more detail in “sequential circuit modeling”) Modeling combinational logic as a process --All signals referenced in process must be in the sensitivity list.

4. Matrix Operations in Excel. Matrix Manipulations ...

www.eng.auburn.eduMatrix Operations in Excel. Matrix Manipulations: Vectors, Matrices, and Arrays. How Excel Handles Matrix Math. Basic Matrix Operations. Solving Systems of Linear Equations. Matrix Manipulations: Vectors, Matrices, and Arrays. In this section we consider the topic of Vectors, Matrices …

Operations, Linear, Excel, Equations, Linear equations, Matrix, Matrices, Manipulation, Matrix operations in excel, Matrix manipulations

EVALUATION OF THE MATURITY METHOD TO ESTIMATE …

www.eng.auburn.eduEVALUATION OF THE MATURITY METHOD TO ESTIMATE CONCRETE STRENGTH ... Jeffery M. Nixon MAY 2006. Research Report ALDOT Research Project 930-590 Evaluation of the Maturity Method to Estimate Concrete Strength Prepared by: Samuel A. Wade Anton K. Schindler Robert W. Barnes ... Nurse-Saul maturity function using a datum temperature of 32°F (0°C ...

Methods, Concrete, Strength, Maturity, Estimates, Usal, Maturity method to estimate, Maturity method to estimate concrete strength

Design template: Robustly design your product to attract ...

www.eng.auburn.eduTemplate 1: For product design and development BEFORE the business plan . 1. A strong product is essential for a strong business plan. ... Design template: Robustly design your product to attract customers . How to use this template? a. Distinguish your product by one or …

Development, Product, Design, Your, Template, Product design and development, Design template, Robustly design your product, Robustly

Related documents

Cortex-M4 Technical Reference Manual

users.ece.utexas.eduCortex-M4 Technical Reference Manual ... arm arm .. ...

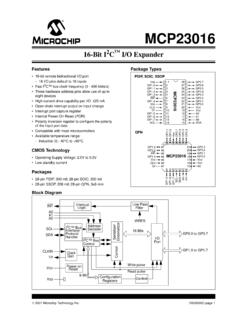

MCP23016 16-Bit I2C I/O Expander - Microchip Technology

ww1.microchip.comDec 08, 2006 · The register block contains the Configuration and Port registers, as shown in Table 1-5. TABLE 1-5: REGISTER SUMMARY Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value on POR Port Registers GP0 GP0.7 GP0.6 GP0.5 GP0.4 GP0.3 GP0.2 GP0.1 GP0.0 0000 0000 GP1 GP1.7 GP1.6 GP1.5 GP1.4 GP1.3 GP1.2 GP1.1 GP0.0 0000 0000

Atmel 8-bit AVR Microcontroller with 2/4/8K Bytes In ...

ww1.microchip.comSix of the 32 registers can be used as three 16-bit indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash Program memory. These added function registers are the 16-bit X-, Y-, and Z-register,

PCA9555 - NXP

www.nxp.com16-bit I2C-bus and SMBus I/O port with interrupt 6.2.2 Registers 0 and 1: Input port registers This register is an input-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Register 3. Writes to …

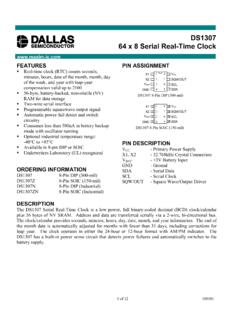

DS1307 64 x 8 Serial Real-Time Clock - SparkFun Electronics

www.sparkfun.comIn the 24-hour mode, bit 5 is the second 10 hour bit (20-23 hours). On a 2-wire START, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to re-read the registers in case of an update of the main registers during ...

SNx4HC595 8-Bit Shift Registers With 3-State Output ...

www.ti.comSNx4HC595 8-Bit Shift Registers With 3-State Output Registers 1 Features • 8-bit serial-in, parallel-out shift • Wide operating voltage range of 2 V to 6 V • High-current 3-state outputs can drive up to 15 LSTTL loads • Low power consumption: 80-μA (maximum) ICC • tpd = 13 ns (typical) • ±6-mA output drive at 5 V

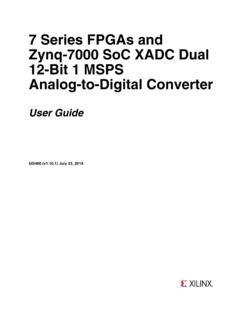

7 Series FPGAs and Zynq-7000 SoC XADC Dual 12-Bit 1 MSPS ...

www.xilinx.comIn Figure 1-1 Zynq-7000 SoC information was added and the control and status registers changed from 32 x 16 bits to 64 x 16 bits. The System Monitor Support section changed to Differences between Virtex-5 and Virtex-6 System Monitors . Functionality for the XADC block in 7 series FPGAs is now defined for previously undefined status registers in