Search results with tag "Sequential"

Chapter 5 Synchronous Sequential Logic

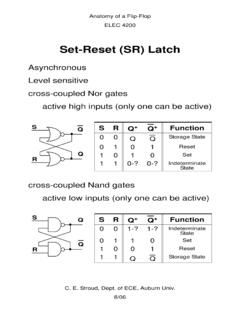

www.cse.iitb.ac.inthe design of asynchronous sequential circuits! Not practical for use in synchronous sequential circuits! Avoid to use latches as possible in synchronous sequential circuits to avoid design problems 5-8 SR Latch! A circuit with two cross-coupled NOR gates or two cross-coupled NAND gates! Two useful states:! S=1, R=0 " set state (Q will become ...

Chapter 6 Synchronous Sequential Circuits

my.ece.utah.eduIn a sequential circuit, the values of the outputs depend on the past behavior of the circuit, as well ... • Asynchronous – where no clock is used . Figure 6.1. The general form of a synchronous sequential circuit. Combinational circuit Flip-flops Clock Q W Z Combinational

DESIGNING SEQUENTIAL LOGIC CIRCUITS

bwrcs.eecs.berkeley.eduDESIGNING SEQUENTIAL LOGIC CIRCUITS Implementation techniques for flip-flops, latches, oscillators, pulse generators, n and Schmitt triggers n Static versus dynamic realization Choosing clocking strategies 7.1 Introduction 7.2 Timing Metrics for Sequential Circuits 7.3 Classification of Memory Elements 7.4 Static Latches and Registers

CHAPTER VIII FINITE STATE MACHINES (FSM)

limsk.ece.gatech.edu• Synchronous sequential system • Behaviour depends on the inputs and outputs at discrete instants of time. • Flip-flops, registers, and latches that are enabled/controlled with a signal derived from clock form a synchronous sequential system. • Asynchronous sequential system • Behaviour depends on inputs at any instant of time.

CHOOSING A MIXED METHODS DESIGN - SAGE …

www.sagepub.comSequential explanatory Sequential exploratory Sequential transformative Concurrent triangulation Concurrent nested Concurrent transformative Author Morgan (1998) Tashakkori and Teddlie (1998) Creswell (1999) Sandelowski (2000) Creswell, Plano Clark, Gutmann, and Hanson (2003) (Continued)

Logix 5000 Controllers Sequential Function Charts ...

literature.rockwellautomation.comThis manual shows how to design and program Sequential Function Charts (SFCs) for Logix 5000 controllers to execute. This manual is one of a set of related manuals that show common procedures for programming and operating Logix 5000 controllers. For a complete list of common procedures manuals, refer to the Logix 5000

Calculation of the Current Transformer Accuracy Limit Factor

library.e.abb.comIn no event shall ABB Oy be liable for direct, indirect, special, incidental or consequential damages of any nature or kind arising from the use of this documen t, nor shall ABB Oy be liable for incidental or con-sequential damages arising from use of any software or hardware described in this document.

Curriculum for Upper Primary Classes (VI – VIII

www.cisce.orgSequential arrangement of learning experiences ( Spiralling) An attempt has been made in this curriculum to design a sequential arrangement of learning experiences, that will provide a spiral of cumulative learning. As they progress through classes, children will revisit certain topics or themes several times, but the depth and

Pipelining & Verilog - Massachusetts Institute of Technology

web.mit.eduSequential Divider Lecture 9 2 Assume the Dividend (A) and the divisor (B) have N bits. If we only want to invest in a single N-bit adder, we can build a sequential circuit that processes a single subtraction at a time and then cycle the circuit N times. This circuit works on unsigned operands; for signed operands one can remember the signs, make

Asynchronous Sequential Circuits - Stanford University

web.stanford.educussed in Section 14.2. In both cases we compute a next state based on current state and input. What’s different is the dynamics of how the current state is updated with the next state. Without a clocked state register, the state of an asynchronous sequential circuit may change at any time (asynchronously).

Self-Attentive Sequential Recommendation

cseweb.ucsd.eduactions used as context. Research in sequential recommendation is therefore largely concerned with how to capture these high-order dynamics succinctly. Markov Chains (MCs) are a classic example, which assume that the next action is conditioned on only the previous action (or previous few), and have been successfully adopted to char-

Chapter 9 Asynchronous Sequential Logic

www.ee.ncu.edu.twAnalysis Procedure Procedure to analyze an asynchronous sequential circuits with SR latches: 1. Label each latch output with Y i and its external feedback path (if any) with y i 2. Derive the Boolean functions for each S i and R i 3. Check whether SR=0 (NOR latch) or S’R’=0 (NAND latch) is satisfied 4. Evaluate Y=S+R’y (NOR latch) or Y=S ...

MIXED METHODS- THEORY AND PRACTICE. SEQUENTIAL ...

www.eajournals.orgMIXED METHODS- THEORY AND PRACTICE. SEQUENTIAL, EXPLANATORY APPROACH Phillip Bowen1, Richard Rose2, Andrew Pilkington2 1Faculty of Business and Law, University of Northampton, UK 2Faculty of Education and Humanities, University of Northampton, UK ABSTRACT: There appears to be a paucity of research undertaken in emotional intelligence

FLIP-FLOPS - California State University, Northridge

www.csun.edumemory 'and is, also the ' building, block for sequential:1qgic circuits. A . primary characteristic' af-sequential lOgiC: , circuj~ is . the ability to "remember" the state of ~e. inputs, i.e., memory. Flip-flops are formed from pairs of logic gates where the gate outputs are fed Into one ,of the inputs of the other gate in the pair. This

Mixed Methods Theory and Practice. Sequential Explanatory ...

www.eajournals.orgsequential, explanatory, mixed methodology is regarded as a popular approach to undertaking research, but not easy to implement (Ivankova, Creswell and Stick, 2016). There are two main categories that emerge: a) mixed method design- that mixes the methods and; b) mixed model

Experiment Sequential Circuits 6 PART A: FLIP FLOPS

www.iium.edu.mySequential Circuits Experiment Objectives-To design a ripple counter using JK flip flop. -To connect a pre-settable counter and observe its operation. -To create different counter module by decoding outputs and loading preset inputs. Introduction A counter is a circuit consisting of a number of Flip Flop and gates

AN ANALYSIS OF STUDENTS’ ANXIETY IN SPEAKING ENGLISH

simki.unpkediri.ac.idsequential explanatory design which quantitative first then followed by qualitative. It is supported by Creswell (2003: 215), “The sequential explanatory strategy is the most straightforward of the . Artikel Skripsi Universitas Nusantara PGRI Kediri Irawati | 14.1.01.08.0152 ...

Econometric Analysis of Cross Section and Panel Data - IPC-IG

ipcig.org11.1.1 Models under Sequential Moment Restrictions 299 11.1.2 Models with Strictly and Sequentially Exogenous Explanatory Variables 305 ... 13.9.1 Models with Strictly Exogenous Explanatory Variables 410 13.9.2 Models with Lagged Dependent Variables 412 13.10 Two-Step MLE 413 Problems 414

The Mixed Methods Appraisal Tool - PCNE

www.pcne.orgExplanatory (quantitative then qualitative) EXAMPLE MIXED STUDIES REVIEW – Sequential exploratory design Review question: Impact of databases on physicians? Step 1: Qualitative synthesis of results of qualitative and quantitative studies (transformation in themes)

Set-Reset (SR) Latch

www.eng.auburn.eduTo verify that a sequential logic circuit will work at the specified clock frequency, fclk, we must consider the clock period, Tp, the ... Asynchronous interfaces lead to metastability (minimize the async interface & double clock data to reduce probability of metastability)

A Stata Plugin for Estimating Group-Based Trajectory ...

ssrc.indiana.eduMar 29, 2013 · the sequential realizations of the elements of Y i , y it ... model( string) probability distribution for the dependent variables (required). Models supported: ... polynomial type (0=intercept, 1=linear, 2=quadratic, 3=cubic) for each group trajectory (required). min( real) minimum value for the censored normal model (required for cnorm).

The importance of inspiring a shared vision - FoNS

www.fons.orgA qualitative research approach within a mixed methods design was used. The overall evaluation study was guided by a sequential explanatory strategy, characterised by collecting and analysing quantitative data in phase one, with a qualitative follow-up in phase two (Creswell and Plano Clark, 2007).

Mixed methods research: expanding the evidence base

ebn.bmj.comExplanatory sequential Quantitative data are collected and analysed first, then qualitative data are collected and analysed to help explain quantitative data QUAN → QUAL AIM: Identify levels of stress among new graduate registered nurses (RNs) working in emergency room (ER) settings QUAN: National survey of new RNs working in ER settings

An Introduction to Mixed Methods Research

sbsrc.unl.eduMar 09, 2007 · An Explanatory Sequential Design Quantitative Data* Number of cigarettes CES-D 6 Qualitative Data* Semi-structured interviews, audio recorded and transcribed * Data collected 10 times over the course of a calendar year for 40 participant s Quantitative Analysis Graphic plot of CES - D6 scores over time for each participant Graphic plot of

The SURVEYSELECT Procedure - Academics | | WPI

www.math.wpi.edusequential PPS sampling with minimum replacement The procedure uses fast, efficient algorithms for these sample selection methods. ... company plans to select a sample of customers from this population, interview the selected customers, and then make inferences about the entire survey population from

The Society of Thoracic Surgeons Expert Consensus for the ...

www.sts.orgthree sequential shocks for VF or the initiation of tem-porary pacing for asystole before ECM, we have consid-ered several factors, as follows. ... asystole will parallel the timing recommendation for defibrillation in VF. In both cases, delay in obtaining the equipment is an indication for immediate ECM.

R. Semiconductor Software 분과 [TA1-R] …

kcs.cosar.or.krDesign and Implementation of Mean Semi-Supervised SVM Using Sequential Minimal Optimization Yongchul Jung, Mingeon Shin, Hounghun Joe, and Sungho Lee Convergence-Signal SoC Research Center, KETI TE1-T-3 09:45-10:00 CBP: Backpropagation with Constraint on Weight Precision Using Pseudo-Lagrange Multiplier Method Guhyun Kim and Doo Seok …

The Sequential Intercept Model - University of South Florida

www.usf.edu, the 114th Congress of the United States of America identified the SIM, specifically the mapping workshop, as a means for promoting community-based strategies to reduce the justice system involvement of people with mental disorders. SAMHSA has supported community-based strategies to improve public health and public safety outcomes

Table 2: Summary of WHO Position Papers - Recommended ...

www.who.intSequential 8 weeks (IPV 1st) 1-2 IPV 2 bOPV 4-8 weeks 4-8 weeks 4-8 weeks IPV 8 weeks 3 4-8 weeks 4-8 weeks (see footnote) ... lack of an explicit co-administration recommendation does not imply that the vaccine cannot be co-administered; further, there are no recommendations

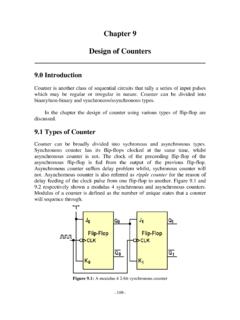

Chapter 9 Design of Counters - Universiti Tunku Abdul Rahman

staff.utar.edu.myChapter 9 Design of Counters _____ 9.0 Introduction Counter is another class of sequential circuits that tally a series of input pulses ... 9.4.2 Design of an Asynchronous Decade Counter Using JK Flip-Flop ... of SR flip-flop shown in Fig. 9.8, the logic of …

UNIT 4 Memory and Programmable Logic

www.pvpsiddhartha.ac.inUNIT 4 Memory and Programmable Logic Random-Access Memory ... In sequential-access memory, the information stored in some medium is not ... AND array and an OR array to provide an AND-OR sum of product implementation. PROM: fixed AND array constructed as a decoder and programmable OR array.

Intro to Verilog - MIT

web.mit.edu-- sequential behavior: always blocks-- pitfalls-- other useful features ... separate behavior from implementation. We need a Hardware Description Language ... known value or when the predicted value is an illegitimate logic value (e.g., due to contention on a tri-state bus). ...

Chapter 18 Sequential Circuits: Flip-flops and Counters

wps.pearsoned.comDesign a counter with the following repeated binary sequence: 0, 4, 2, 1, 6. Use T flip-flops. Solution: Step 1: Since it is a 3-bit counter, the number of flip-flops required is three. Step 2: Let the type of flip-flops be RS flip-flops. Step 3: Let the three flip-flops be A, B and C. Step 4: The state table is as shown in Table 3.1.

Basic Nameplate Information - Sustainable Farming on the ...

sustainable-farming.rutgers.edu00236 – Sequential number assigned on manufacturing date D – Manufacturing location letter code 05 – Year manufactured 045 – Day of the year manufactured (045 = Feb 14) A light fixture model number might be SH 400MP A16 240 HEB WGA16, where: SH - Fixture series 400MP – Lamp type A16 – Reflector style 240 – Voltage

An overview of dyscalculia - ed

files.eric.ed.gov• Photocopy mathematics books, which are generally difficult to read because of the interspersement of diagrams, tables, and charts, with the relevant sections placed in a more sequential order. • Separate multi-step problems into small, manageable steps. • Use a line reader, if available, to highlight a line of work and fade the

TLC555 LinCMOS Timer datasheet (Rev. I) - TI.com

www.ti.com• Sequential timing • Time delay generation • Pulse width modulation • Pulse position modulation • Linear ramp generator 3 Description The TLC555 is a monolithic timing circuit fabricated using the TI LinCMOS™ process. The timer is fully compatible with CMOS, TTL, and MOS logic and operates at frequencies up to 2 MHz. Because of its

Mixed-Methods Research Methodologies

files.eric.ed.govSequential Explanatory Strategy The collection and analysis of quantitative data followed by the collection and analysis of qualitative data. Equal priority is given to the two phases. Data are integrated during interpretation. Primary focus is to explain quantitative results by exploring certain results in more detail or

Synchronous Resets? Asynchronous Resets? I am so …

www.sunburst-design.comsynchronous or asynchronous resets, will every flip-flop receive a reset, how will the reset tree be laid out and buffered, how to verify timing of the reset tree, how to functionally test the reset with test scan vectors, and how to ... In Verilog, all assignments made inside the always block modeling an inferred flip-flop (sequential logic ...

Examples of Solved Problems for Chapter3,5,6,7,and8

www.eecg.utoronto.casequential in this document. Example 3.9 Problem: We introduced standard cell technology in section 3.7. In this technology, circuits are built by interconnecting building-block cells that implement simple functions, like basic logic gates. A commonly used type of standard cell are the and-or-invert (AOI) cells, which can be efficiently

EMBEDDED SYSTEM DESIGN - Bharath Institute of Higher ...

www.bharathuniv.ac.inAt the top, we find VLSI circuits comprising of significant pieces of functionality: microprocessor, microcontrollers, FPGA‘s, CPLD, and ASIC. Our study of hardware side of embedded systems begins with a high level view of the ... It is an example of sequential digital logic, as it …

ELEVATOR CONTROL CIRCUIT

eie.uonbi.ac.kecircuits. In a synchronous sequential circuit, changes of state are only allowed to happen at times synchronous to a special timing signal, called the clock. The simplest synchronous circuit is a one-bit storage element, which is also referred to as a flip-flop. There are four popular types of flip-flops i.e. JK, D, T and SR flip-flops ...

Introduction to School Health Programs

www.doe.virginia.govRecommendation Essential Elements. ... A planned, sequential K-12 curriculum that provides cognitive content and learning experiences in a variety of activity areas. ♦ Promotes each student’s optimum physical, mental, emotional, and social development through a variety of

Sequential Logic Implementation

inst.eecs.berkeley.eduSequential Logic Implementation Models for representing sequential circuits Abstraction of sequential elements Finite state machines and their state diagrams Inputs/outputs Mealy, Moore, and synchronous Mealy machines Finite state machine design procedure

Sequential Pattern Mining - College of Computing

faculty.cc.gatech.eduRastogi, Shim [VLDB’99]; Pei, Han, Wang [CIKM’02]) • Mining closed sequential patterns: CloSpan (Yan, Han & Afshar [SDM’03]) 9 ... – Disk-based random accessing is very costly • Suggested Approach: – Integration of physical and pseudo-projection – Swapping to pseudo-projection when the data set

Sequential Minimal Optimization: A Fast Algorithm for ...

www.microsoft.com3 where xi is the ith training example, and yi is the correct output of the SVM for the ith training example. The value yi is +1 for the positive examples in a class and –1 for the negative examples. Using a Lagrangian, this optimization problem can be converted into a dual form which is a QP problem where the objective function Ψ is solely dependent on a set of Lagrange multipliers αi,

Sequential System Design Using ASM Charts

www.xilinx.comDigital systems typically consist of datapath processing and the control path. The control path is implemented using state machines which can be realized using state graphs. As the control path (behavior) of the system becomes complex, it becomes increasingly difficult to design the control path using the state graph technique.

Similar queries

Sequential, Asynchronous sequential, Asynchronous, A synchronous sequential, SEQUENTIAL LOGIC, Implementation, CHOOSING A MIXED METHODS DESIGN, SAGE, Sequential explanatory Sequential, Logix 5000 Controllers Sequential Function Charts, Function, Controllers, Consequential, Con-sequential, Curriculum for Upper Primary Classes, Massachusetts Institute of Technology, Bit adder, Section, Sequential recommendation, Markov Chains, Chapter 9 Asynchronous Sequential Logic, Analysis, Path, THEORY, THEORY AND PRACTICE. SEQUENTIAL, EXPLANATORY APPROACH, Research, California State University, Northridge, Circuits, Theory and Practice. Sequential Explanatory, Explanatory, Sequential Circuits, ANXIETY, SPEAKING, Sequential Explanatory, The Mixed Methods Appraisal Tool, Stata, Model, Intercept, The importance of inspiring a shared vision, Approach, Mixed methods research, Explanatory Sequential, The SURVEYSELECT Procedure, Sampling, Plans, Recommendation, Sequential Minimal Optimization, The Sequential Intercept Model, University of South Florida, 114th Congress, Public, Chapter 9, Logic, Chapter 18 Sequential Circuits: Flip-flops and, Design, Flip, Basic Nameplate Information, Mathematics, Datasheet, Mixed-Methods Research Methodologies, Synchronous Resets? Asynchronous Resets? I, Flops, Sequential Logic Implementation, Sequential Pattern Mining, Random, Sequential System Design Using ASM Charts, Systems, Control

![R. Semiconductor Software 분과 [TA1-R] …](/cache/preview/e/7/7/c/8/c/f/8/thumb-e77c8cf85e209db3e104605e3f98ceb3.jpg)