Transcription of AOD4186 N-Channel Enhancement Mode Field …

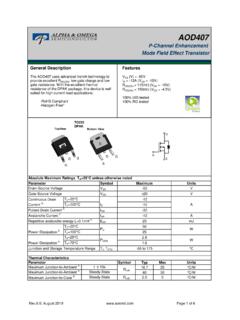

1 General DescriptionFeatures(VGS = 10V)(VGS = 10V)(VGS = ) - RoHS Compliant100% UIS Tested! - Halogen Free100% Rg Tested!SymbolVDSVGSIDMIAREARTJ, = 35 ARDS(ON) < 15m TC=25 C2470 Pulsed Drain Current CContinuous Drain Current GJunction and Storage Temperature Range-55 to 175 CThermal CharacteristicsUnitsMaximum Junction-to-Ambient At 10s C/WParameterR JAVV 20 Gate-Source VoltageDrain-Source Voltage40 AOD4186N-Channel Enhancement Mode Field Effect TransistorMaximumUnitsParameterAbsolute Maximum Ratings TA=25 C unless otherwise notedThe AOD4186 combines advanced trench MOSFET technology with a low resistance package to provide extremely low RDS(ON). This device is ideal for low voltage inverter (ON) < 19m VDS (V) =40 VRepetitive avalanche energy L= CmJAvalanche Current C8 Continuous Drain Current2910 AATA=25 CIDSMATA=70 CID3527TC=25 C TC=100 C Power Dissipation BPDWP ower Dissipation APDSMWTA=70 CMaximum Junction-to-CaseSteady-State C/WSteady-State C/WMaximum Junction-to-Ambient A D G TO-252D-PAKTop View S Bottom View D G S G D SAlpha & Omega Semiconductor, , VGS=0V 1TJ=55 C5 IGSS100nAVGS(th)Gate Threshold (ON) Qg(10V) ( ) (on)6nstr12nstD(off)26nstf7nstrr91215nsQ rr243138nCRev 1 : May-09 COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED.

2 AOS DOES NOT ASSUME ANY LIABILITY ARISINGOUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT Diode Reverse Recovery ChargeIF=20A, dI/dt=500A/ sMaximum Body-Diode Continuous CurrentInput CapacitanceOutput CapacitanceTurn-On DelayTimeDYNAMIC PARAMETERSTurn-On Rise TimeTurn-Off DelayTimeVGS=10V, VDS=20V, RL= , RGEN=3 Gate resistanceVGS=0V, VDS=0V, f=1 MHzTurn-Off Fall TimeTotal Gate ChargeVGS=10V, VDS=20V, ID=20 AGate Source ChargeGate Drain ChargeTotal Gate Chargem IS=1A,VGS=0 VVDS=5V, ID=20 AVGS= , ID=15A Forward TransconductanceDiode Forward VoltageRDS(ON)Static Drain-Source On-ResistanceIDSS AVDS=VGS ID=250 AVDS=0V, VGS= 20 VZero Gate Voltage Drain CurrentGate-Body leakage currentElectrical Characteristics (TJ=25 C unless otherwise noted)STATIC PARAMETERSP arameterConditionsBody Diode Reverse Recovery TimeDrain-Source Breakdown VoltageOn state drain currentID=250 A, VGS=0V VGS=10V, VDS=5 VVGS=10V, ID=20A Reverse Transfer CapacitanceIF=20A, dI/dt=500A/ sVGS=0V, VDS=20V, f=1 MHzSWITCHING PARAMETERSA.

3 The value of R JA is measured with the device mounted on 1in2 FR-4 board with 2oz. Copper, in a still air environment with TA =25 C. The Power dissipation PDSM is based on R JA and the maximum allowed junction temperature of 150 C. The value in any given application depends on the user's specific board design, and the maximum temperature of 175 C may be used if the PCB allows The power dissipation PD is based on TJ(MAX)=175 C, using junction-to-case thermal resistance, and is more useful in setting the upper dissipation limit for cases where additional heatsinking is used. C. Repetitive rating, pulse width limited by junction temperature TJ(MAX)=175 C. Ratings are based on low frequency and duty cycles to keep initial TJ =25 The R JA is the sum of the thermal impedence from junction to case R JC and case to The static characteristics in Figures 1 to 6 are obtained using <300 s pulses, duty cycle These curves are based on the junction-to-case thermal impedence which is measured with the device mounted to a large heatsink, assuming a maximum junction temperature of TJ(MAX)=175 C.

4 The SOA curve provides a single pulse rating. G. The maximum current rating is limited by bond-wires. H. These tests are performed with the device mounted on 1 in2 FR-4 board with 2oz. Copper, in a still air environment with TA=25 C. Alpha & Omega Semiconductor, ELECTRICAL AND THERMAL CHARACTERISTICS1752100184002040608001234 56 VGS(Volts)Figure 2: Transfer Characteristics (Note E)ID(A)8101214161820051015202530ID (A)Figure 3: On-Resistance vs. Drain Current and Gate Voltage (Note E)RDS(ON) (m ) + + + (Volts)Figure 6: Body-Diode Characteristics (Note E)IS (A)25 C125 ( C)Figure 4: On-Resistance vs. Junction Temperature (Note E)Normalized On-ResistanceVGS= (Volts)Figure 5: On-Resistance vs. Gate-Source Voltage (Note E)RDS(ON) (m )25 C125 CVDS=5 VVGS= C125 C020406080012345 VDS (Volts)Fig 1: On-Region Characteristics (Note E)ID (A)VGS= & Omega Semiconductor, ELECTRICAL AND THERMAL CHARACTERISTICS1752100184002468100510152 0Qg (nC)Figure 7: Gate-Charge CharacteristicsVGS (Volts)0300600900120015000 10203040 VDS (Volts)Figure 8: Capacitance CharacteristicsCapacitance (pF) Width (s)Figure 10: Single Pulse Power Rating Junction-to-Case (Note F)Power (W) Width (s)Figure 11: Normalized Maximum Transient Thermal Impedance (Note F)Z JC Normalized Transient Thermal ResistanceCossCrssVDS=20 VID=20 ASingle PulseD=Ton/TTJ,PK=TC+ JCTonTPDIn descending orderD= , , , , , , single pulseTJ(Max)=175 CTC=25 C10 (Volts)ID (Amps)Figure 9.

5 Maximum Forward Biased Safe Operating Area (Note F)10 s10ms1msDCRDS(ON) limitedTJ(Max)=175 CTC=25 C100 sR JC=3 C/WAlpha & Omega Semiconductor, ELECTRICAL AND THERMAL Width (s)Figure 16: Normalized Maximum Transient Thermal Impedance (Note H)Z JA Normalized Transient Thermal ResistanceSingle PulseD=Ton/TTJ,PK=TA+ JATonTPDIn descending orderD= , , , , , , single in avalanche, tA (s)Figure 12: Single Pulse Avalanche capability (Note C)IAR(A) Peak Avalanche Current 01020304050600255075100125150175 TCASE ( C)Figure 13: Power De-rating (Note F)Power Dissipation (W)01020304050600255075100125150175 TCASE ( C)Figure 14: Current De-rating (Note F)Current rating ID(A)TA=25 Width (s)Figure 15: Single Pulse Power Rating Junction-to-Ambient (Note H)Power (W)TA=25 CTA=150 CTA=100 CTA=125 CR JA=50 C/WAlpha & Omega Semiconductor, +VDCIgVdsDUT-+VDCVgsVgs10 VQgQgsQgdChargeGate Charge Test Circuit & Waveform-+VDCDUTVddVgsVdsVgsRLRgVgsVds10 %90%Resistive Switching Test Circuit & Waveformsttrd(on)tontd(off)tftoffVddVgsI dVgsRgDUT-+VDCLVgsVdsIdVgsBVIU nclamped Inductive Switching (UIS) Test Circuit & WaveformsIgVgs-+VDCDUTLVdsVgsVdsIsdIsdDi ode Recovery Test Circuit & WaveformsVds -Vds +IFARDSS2E = 1/2 LIdI/dtIRMrrVddVddQ = - IdtARARtrrAlpha & Omega Semiconductor.