Functions, Procedures, and Testbenches - Xilinx

VHDL supports two types of delay modeling: (i) inertial and (ii) transport. The inertial delay is the delay that a gate or circuit may experience due to the physical nature of the gate or circuit. The inertial delay is also used to determine if the input has an effect on the gate or circuit. If the input does not remain

Tags:

Procedures, Functions, Circuit, Xilinx, Vhdl, And testbenches, Testbenches

Information

Domain:

Source:

Link to this page:

Please notify us if you found a problem with this document:

Documents from same domain

Accelerating OpenCV Applications with Zynq-7000 …

www.xilinx.comReference Design XAPP1167 (v3.0) June 24, 2015 www.xilinx.com 2 The design flow for this application note generally follows the steps below: 1. Develop and execute an OpenCV application on Desktop.

Applications, With, Accelerating, Xilinx, Accelerating opencv applications with zynq, Opencv, Zynq

Xilinx XAPP1113 Designing Efficient Digital Up and …

www.xilinx.comIntroduction XAPP1113 (v1.0) November 21, 2008 www.xilinx.com 2 R • DDC design files for multi-channel MRI, targeting both Virtex-5 and Spartan®-DSP

Efficient, Designing, Digital, Xilinx, Xilinx xapp1113 designing efficient digital up and, Xapp1113

Xilinx DS060 Spartan and Spartan-XL FPGA …

www.xilinx.comSpartan and Spartan-XL FPGA Families Data Sheet 2 www.xilinx.com DS060 (v2.0) March 1, 2013 Product Specification R Product Obsolete/Under Obsolescence General Overview Spartan series FPGAs are implemented with a regular, flex-

Zynq-7000 All Programmable SoC Software …

www.xilinx.comZynq-7000 All Programmable SoC Software Developers Guide UG821 (v12.0) September 30, 2015

Developer, Guide, Software, Programmable, Software developers guide

Zynq-7000 SoC Data Sheet: Overview (DS190) - All …

www.xilinx.comZynq-7000 SoC Data Sheet: Overview DS190 (v1.11.1) July 2, 2018 www.xilinx.com Product Specification 3 Programmable Logic Xilinx 7 Series Programmable Logic

Overview, Programmable, Programmable logic, Logic, Xilinx, Programmable logic xilinx

7 Series FPGAs Data Sheet: Overview (DS180)

www.xilinx.com7 Series FPGAs Data Sheet: Overview DS180 (v2.6) February 27, 2018 www.xilinx.com Product Specification 2 Spartan-7 FPGA Feature Summary Table 2: Spartan-7 FPGA Feature Summary by Device

Product Obsolete/Under Obsolescence …

www.xilinx.comEfficient Shift Registers, LFSR Counters, and Long Pseudo-Random Sequence Generators 2 XAPP 052 July 7,1996 (Version 1.1) Divide-By 5 to 16 Counter in Two CLBs

XILINX ARTIX-7 FPGAS: A NEW PERFORMANCE …

www.xilinx.comKey Capability Overview . Smallest Package • Low-cost, wire-bond, chip-scale BGA packaging • Available in a 10x10mm package for maximum system integration

Platform Flash In-System Programmable …

www.xilinx.comPlatform Flash In-System Programmable Configuration PROMs DS123 (v2.19) June 6, 2016 www.xilinx.com Product Specification 2 R When the FPGA is in Master Serial mode, it generates a

Spartan-3AN FPGA Family Data Sheet (DS557) - Xilinx

www.xilinx.comSpartan-3AN FPGA Family: Introduction and Ordering Information DS557 (v4.2) June 12, 2014 www.xilinx.com Product Specification 3 Architectural Overview

Related documents

ECE 410: VLSI Design Course Lecture Notes

www.egr.msu.eduDesign Rules Abstract High-level Model VHDL, Verilog HDL Top Down Design Bottom Up Design Functional Simulation Functional/Timing/ Performance Specifications. ECE 410, Prof. F. Salem Lecture Notes Page 2.6 Integrated Circuit Technologies • Why does CMOS dominate --Now ? – other technologies • passive circuits

Lecture, Notes, Design, Course, Circuit, Vlsi, Vhdl, Vlsi design course lecture notes

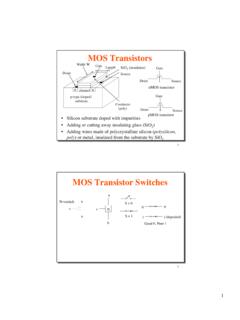

MOS Transistors - Duke Electrical and Computer Engineering

people.ee.duke.edu– Pull-up circuit corresponds to pull-up graph 11 21 Graph Models a b c Gnd d a b d c Pull-down circuit Gnd ... Gate-Level Mux Design • How many transistors are needed? 20 14 27 ... e.g. VHDL, Verilog • Example: Consider the carry function c o = ab + bc + c i a 22 43

Modeling Registers and Counters - Xilinx

www.xilinx.comD input, reset, load, and output. Verify the design in hardware. 1-1-1. Open Vivado and create a blank project called lab6_1_1. 1-1-2. Create and add the VHDL module that will model the 4-bit register with synchronous reset and load. Use the code provided in the above example. 1-1-3. Develop a testbench and simulate the design. Analyze the output.

Design, Modeling, Registers, Counter, Xilinx, Vhdl, Modeling registers and counters

Verilog Tutorial - UMD

classweb.ece.umd.eduindustry for designing the Hardware. Verilog allows us to design a Digital design at Behavior Level, Register Transfer Level (RTL), Gate level and at switch level. Verilog allows hardware designers to express their designs with behavioral constructs, deterring the details of implementation to a later stage of design in the final design.

Solution of Homework#06 - Naresuan University

www.ecpe.nu.ac.thD, E and F. So you have to design the code converter circuit to convert binary code inputs to seven-segment code outputs. If the circuit has an active-high “lamp test” input which force all LEDs on, and the active-low “blank input” input which force all LEDs off except “lamp test” is asserted. Show the truth table, simplified AND-OR

Sample PhD CV Postdoctoral Research - Duke University

studentaffairs.duke.edu• Integrated Circuit Engineering—Silicon Processing • Semiconductor Devices for IC • Quantum Mechanics • Solid State Physics • Optical Communication System • Advanced Digital System Design. PUBLICATIONS: • A Nucleation-Growth Model of Nanowires Produced by the Vapor-Liquid-Solid Process, P.R.A.and A.B.Foushee (inpreparation)

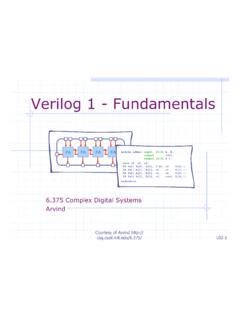

Verilog 1 - Fundamentals - University of California, San Diego

cseweb.ucsd.eduVerilog, VHDL, SystemVerilog C, C++, SystemC Behavioral RTL Verilog, VHDL, SystemVerilog MATLAB Simulators and other tools are available at all levels but not compilers from the behavioral level to RTL

VHDL Test Bench Tutorial - University of Pennsylvania

www.seas.upenn.eduUpdated February 12, 2012 3 Tutorial Procedure The best way to learn to write your own VHDL test benches is to see an example. For the purposes of this tutorial, we will create a test bench for the four-bit adder used in Lab 4. For the impatient, actions that you need to perform have key words in bold. 1.