Transcription of Switched-Capacitor Integrator

1 EECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 1EE247 Lecture 10 Switched-Capacitor filters (continued) Switched-Capacitor integrators DDI & LDI integrators Effect of parasitic capacitance Bottom-plate Integrator topology Switched-Capacitor resonators Bandpass filters Lowpass filters Switched-Capacitor filter design considerations Termination implementation Transmission zero implementation Limitations imposed by non-idealitiesEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H.

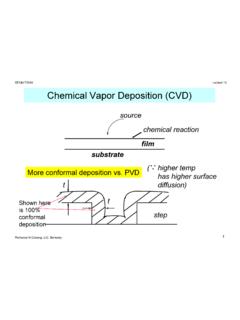

2 K. Page 2 Switched-Capacitor Integrator -+VinVo 1 2 CICs-+VinVo 1 CICs-+VinVo 2 CICs 1 2T=1/fs 1 High CsCharged to Vin 2 High Charge transferred fromCstoCIEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 3 Switched-Capacitor IntegratorOutput Sampled on 1 1 2 1 2 1 VinVoVCsClockVo1-+VinVo1 1 2 CICs 1 VoEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 4 Switched-Capacitor Integrator 1 2 1 2 1 VinVoVsClockVo1 1 Qs [(n-1)Ts]= CsVi [(n-1)Ts] , QI [(n-1)Ts] = QI [(n-3/2)Ts] 2 Qs [(n-1/2) Ts] = 0 , QI[(n-1/2) Ts] = QI[(n-1) Ts] + Qs[(n-1) Ts] 1 _ Qs[nTs] = CsVi [nTs] , QI[nTs] = QI[(n-1) Ts] + Qs[(n-1) Ts]SinceVo1= - QI/CI& Vi= Qs/ Cs CIVo1(nTs) = CIVo1[(n-1) Ts] -CsVi[(n-1) Ts] (n-1)TsnTs(n-1/2)Ts(n+1)Ts(n-3/2)Ts(n+1/ 2)TsEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H.

3 K. Page 5 Switched-Capacitor IntegratorOutput Sampled on 1sIsI1s1 IososssIIinCosossinCC11ooinCCC1inCV(nT) CVCV(n 1)T(n 1)TV(nT)VV(n 1)T(n 1)TV (Z) Z V (Z) ZV (Z)VoZ(Z )ZV = = = = DDI (Direct-Transform Discrete Integrator )-+VinVo1 1 2 CICs 1 VoEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 6 Switched-Capacitor Direct-Transform Discrete Integrator1s1Is1 ICC1inCC1 Voz(z)zVz = = -+VinVo 1 2 CICs 1 EECS 247 Lecture 10 Switched-Capacitor Filters 2008 H.

4 K. Page 7 DDI Switched-Capacitor IntegratorCIIdeal IntegratorMagnitude ErrorPhase Error()()1s1 IjT/2ssjTjT/2 jT/2 IIsIsICjTC1injjCCCC1 CjT/2 CCjT/2 CjTVoz(z),z ezVeee1since: sin2jeee1je2sinT/2T/21esinT/2 = = = = == = -+VinVo 1 2 CICs 1 EECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 8 DDI Switched-Capacitor IntegratorExample: Mag. & phase error for:1- f / fs=1/12 Mag. error = 1% or error=15 degreeQintg= f / fs=1/32 Mag.

5 Error= or error= degreeQintg= +VinVo 1 2 CICs 1 DDI Integrator : magnitude error no problemphase error major problemEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 95thOrder Low-Pass switched Capacitor Filter Built with DDI IntegratorsExample: 5th Order Elliptic FilterSingularities pushed towards RHP due to Integrator excess phases-planeFine Viewj Ideal PoleIdeal Zeros-planeCoarse Viewj s- sDDI PoleDDI ZeroEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H.

6 K. Page 10 Frequency (Hz) switched Capacitor Filter Build with DDI Integrator () jHsf/2sf2fsfContinuous-TimePrototypeSC DDI basedFilterPassbandPeakingZeros lost!EECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 11 Switched-Capacitor Integrator Output Sampled on 2CI-+VinVo2 1 2 CICs 2 Sample output clock cycle earlier Sample output on 2 VoEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 12 1 Qs [(n-1)Ts]= CsVi [(n-1)Ts] , QI [(n-1)Ts] = QI[(n-3/2)Ts] 2 Qs [(n-1/2) Ts] = 0 , QI[(n-1/2) Ts] = QI[(n-3/2) Ts] + Qs[(n-1) Ts] 1 _ Qs[nTs] = CsVi [nTs] , QI[nTs] = QI[(n-1) Ts] + Qs[(n-1) Ts] 2 Qs [(n+1/2) Ts] = 0 , QI[(n+1/2) Ts] = QI[(n-1/2) Ts] + Qs[n Ts] 1 2 1 2 1 VinVo2 VsClock(n-1)TsnTs(n-1/2)Ts(n+1)Ts(n-3/2) TsSwitched-Capacitor Integrator Output Sampled on 2(n+1/2)

7 TsEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 13QI[(n+1/2) Ts] = QI[(n-1/2) Ts] + Qs[n Ts]Vo2= - QI/CI& Vi= Qs/ Cs CIVo2 [(n+1/2) Ts] = CIVo2[(n-1/2) Ts] -CsVi[n Ts]Using the z operator rules: CIVo2 z1/2 = CIVo2 z-1/2-CsVi1/ 2s1 ICC1inVo2z(z)zV = Switched-Capacitor Integrator Output Sampled on 2 1 2 1 2 1 VinVoVsClock(n-1)TsnTs(n-1/2)Ts(n+1)Ts(n -3/2)TsEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 14 LDI Switched-Capacitor Integrator ()()1/ 2s1 IjT/2ses1jTj T/2j T/2 IIsIsICjTC1zinCCCC1 CCCCjTVo2z(z),z eVeee1j2sinT/2T/21sinT/2 + = == = = = CIIdeal IntegratorMagnitude ErrorNo Phase Error!

8 For signals at frequencies << sampling freq. Magnitude error negligible-+VinVo2 1 2 CICs 2 LDILDI (Lossless Discrete Integrator ) same as DDI but output is sampled clock cycle earlierEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 15 Switched-Capacitor Filter Built with LDI Integrators() jHZeros PreservedFrequency (Hz)2fsffsfs /2 EECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 16 Switched-Capacitor IntegratorParasitic Capacitor SensitivityEffect of parasitic capacitors :1- Cp1 - driven by opamp Cp2 - at opamp virtual gnd Cp3 Charges to Vin & discharges into CI Problem parasitic capacitor sensitivity-+VinVo 1 2 CICsCp3Cp2Cp1 EECS 247 Lecture 10 Switched-Capacitor Filters 2008 H.

9 K. Page 17 Parasitic InsensitiveBottom-Plate Switched-Capacitor IntegratorSensitive parasitic cap. Cp1 rearrange circuit so that Cp1does not charge/discharge 1=1 Cp1grounded 2=1 Cp1at virtual groundSolution: Bottom plate capacitor integratorVi+Cs-+VoCICp1Cp2 1 2Vi-EECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 18 Bottom Plate Switched-Capacitor Integrator12121ss11 IIss11 IICCzzCC1z1zCCz1CC1z1z Note: Different delay from Vi+ &Vi- to either output Special attention needed for input/output connections to ensure LDI realizationVi+Cs-+VoCI 1 2Vi-Vi+on 1Vi-on 2Vo1on 1Vo2on 2 1 2Vo2Vo1 Output/Inputz-TransformEECS 247 Lecture 10 Switched-Capacitor Filters 2008 H.

10 K. Page 19 Bottom Plate Switched-Capacitor Integratorz-Transform Model121211111zz1z1zz11z1z 121z1z 12z Input/Output z-transformVi+Cs-+VoCI 1 2Vi- 1 2Vo2Vo1Vi+Vi-12z+Vo2Vo1 LDIsICCsICC EECS 247 Lecture 10 Switched-Capacitor Filters 2008 H. K. Page 20 LDI Switched-Capacitor Ladder FilterCsCI121z1z -++ -+ -31s 41s 51s 12z 12z+12z+12z CsCI CsCI CsCI CsCICsCIDelay around Integrator loop is (z-1/2. z+1/2=1) LDI function121z1z 121z1z 12z 12z+EECS 247 Lecture 10 Switched-Capacitor Filters 2008 H.