PCA9555 - NXP

16-bit I2C-bus and SMBus I/O port with interrupt 6.2.2 Registers 0 and 1: Input port registers This register is an input-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Register 3. Writes to …

Download PCA9555 - NXP

Information

Domain:

Source:

Link to this page:

Please notify us if you found a problem with this document:

Documents from same domain

AN10441 Level shifting techniques in I2C-bus design

www.nxp.comDocument information AN10441 Level shifting techniques in I2C-bus design Rev. 01 — 18 June 2007 Application note Info Content Keywords I2C-bus, level shifting Abstract Logic level shifting may be required when interfacing legacy devices with

Notes, Applications, Levels, Technique, Shifting, Application note, An10441 level shifting techniques in, An10441

AN3234: Washing Machine Three-Phase AC …

www.nxp.comWashing Machine Three-Phase AC Induction Motor Drive, Rev. 0 Indirect Vector Control 4 Freescale Semiconductor If you are looking for more theory on the field ...

1. General description - nxp.com

www.nxp.com1. General description The TJA1044 is part of the Mantis family of high-speed CAN transceivers. It provides an interface between a Controller Area Network (CAN) protocol controller and the physical

General, Descriptions, General description, General description nxp

PCA9570 Remote 4-bit general purpose outputs for 1 MHz …

www.nxp.com1. General description The PCA9570 is a CMOS device that provides 4 bits of General Purpose parallel Output (GPO) expansion in low voltage processor and handheld battery powered mobile

General, Purpose, Remote, Output, General purpose, Pca9570 remote 4 bit general purpose outputs for, Pca9570

P82B96 Dual bidirectional bus buffer - nxp.com

www.nxp.com1. General description The P82B96 is a bipolar IC that creates a non-latching, bidirectional, logic interface between the normal I2C-bus and a range of other bus configurations.It can interface

S32K144 EVB Quick Start Guide - NXP Semiconductors

www.nxp.comJ14 SWD connector. 3 EXTERNAL USE S32K144 EVBFeatures: ... USB connector of the USB cable to micro-B port J7 on the S32K144EVB. ... Windows, Linux and Mac operating systems. Using the MSD Flash Programmer 1. Locate the .srec file of your project , file is under the

Three-Phase BLDC Motor Sensorless Control Using …

www.nxp.comThis document describes the design of a three-phase brushless DC motor (BLDC motor) drive based on Freescale’s MC56F8013 and MC56F8023 dedicated motor control device. Brushless DC motors are popular in a wide application area.

Phases, Using, Control, Motor, Three, Sensorless, Brushless, Brushless dc, Three phase brushless dc, Motor sensorless control using

AN11443 BFU550XR ISM 433 MHz LNA design - nxp.com

www.nxp.comAN11443 BFU550XR ISM 433 MHz LNA design Rev. 1 — 23 January 2014 Application note . Document information Info Content Keywords BFU520, BFU530, BFU550 series, ISM-band, 433MHz 866MHz Abstract This document describes an ISM Frequency LNA design on BFU5xxXR Starter kit

DSP56156 16-Bit Digital Signal Processor - nxp.com

www.nxp.comThe DSP56156 is a general-purpose MPU-style Digital Signal Processor (DSP). On a single semi- conductor chip, the DSP56156 comprises a very efficient 16-bit digital signal processing core, pro-

Processor, Processing, Signal, Digital, Digital signal processing, Digital signal processor

SAA7706H Car radio Digital Signal Processor (DSP)

www.nxp.comCar radio Digital Signal Processor (DSP) SAA7706H This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in _white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

Processor, Radio, Signal, Digital, Car radio digital signal processor

Related documents

Cortex-M4 Technical Reference Manual

users.ece.utexas.eduCortex-M4 Technical Reference Manual ... arm arm .. ...

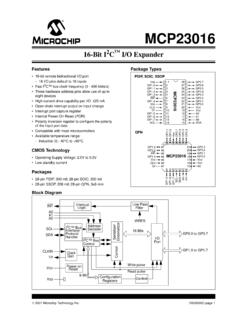

MCP23016 16-Bit I2C I/O Expander - Microchip Technology

ww1.microchip.comDec 08, 2006 · The register block contains the Configuration and Port registers, as shown in Table 1-5. TABLE 1-5: REGISTER SUMMARY Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value on POR Port Registers GP0 GP0.7 GP0.6 GP0.5 GP0.4 GP0.3 GP0.2 GP0.1 GP0.0 0000 0000 GP1 GP1.7 GP1.6 GP1.5 GP1.4 GP1.3 GP1.2 GP1.1 GP0.0 0000 0000

Atmel 8-bit AVR Microcontroller with 2/4/8K Bytes In ...

ww1.microchip.comSix of the 32 registers can be used as three 16-bit indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash Program memory. These added function registers are the 16-bit X-, Y-, and Z-register,

C programming for embedded system applications

www.eng.auburn.eduPORTA = c | 0x01; // write c to PORTA with bit 0 set to 1 Fall 2014 - ARM Version ELEC 3040/3050 Embedded Systems Lab (V. P. Nelson) Example of µC register address definitions in

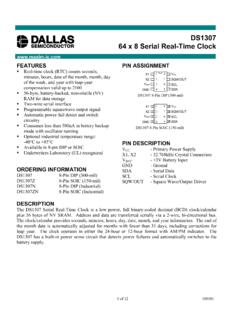

DS1307 64 x 8 Serial Real-Time Clock - SparkFun Electronics

www.sparkfun.comIn the 24-hour mode, bit 5 is the second 10 hour bit (20-23 hours). On a 2-wire START, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to re-read the registers in case of an update of the main registers during ...

SNx4HC595 8-Bit Shift Registers With 3-State Output ...

www.ti.comSNx4HC595 8-Bit Shift Registers With 3-State Output Registers 1 Features • 8-bit serial-in, parallel-out shift • Wide operating voltage range of 2 V to 6 V • High-current 3-state outputs can drive up to 15 LSTTL loads • Low power consumption: 80-μA (maximum) ICC • tpd = 13 ns (typical) • ±6-mA output drive at 5 V

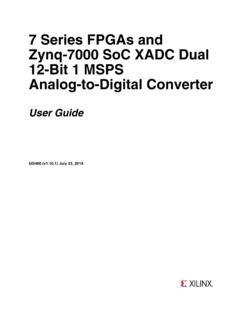

7 Series FPGAs and Zynq-7000 SoC XADC Dual 12-Bit 1 MSPS ...

www.xilinx.comIn Figure 1-1 Zynq-7000 SoC information was added and the control and status registers changed from 32 x 16 bits to 64 x 16 bits. The System Monitor Support section changed to Differences between Virtex-5 and Virtex-6 System Monitors . Functionality for the XADC block in 7 series FPGAs is now defined for previously undefined status registers in