Search results with tag "Lvpecl"

Interfacing Between LVPECL, VML, CML and LVDS Levels

www.ti.comInterfacing Between LVPECL, VML, CML, and LVDS Levels 5 3.1 LVPECL Interface Structures LVPECL is derived from ECL and PECL and typically uses 3.3 V and ground supply voltage. The current Texas Instruments serial gigabit solution device that has an integrated LVPECL driver is the TNETE2201 device. 3.1.1 LVPECL Output Stage

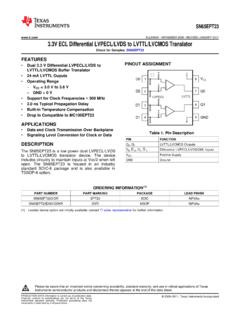

NOVEMBER 2009 3.3V ECL Differential LVPECL/LVDS to LVTTL ...

www.ti.com1 8 2 7 3 6 4 5 D0 Q0 Q1 V CC D0 D1 D1 GND LVPECL LVTTL + + + + + SN65EPT23 www.ti.com SLLS969A –NOVEMBER 2009–REVISED JANUARY 2011 3.3V ECL Differential LVPECL/LVDS to LVTTL/LVCMOS Translator

第第1章 1章 のI/O端子を 理解して使っていますか

www.cqpub.co.jpLVTTL low voltage TTL(低電圧TTL) 3.3 ― LVTTL なし ... LVPECL low valtage positive emitter coupled logic 2.5 ― LVPECL_25 なし ...

Two Selectable Inputs, 8 LVPECL Outputs ... - …

www.analog.comTwo Selectable Inputs, 8 LVPECL Outputs, SiGe Clock Fanout Buffer Data Sheet ADCLK948 Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable.

AC-Coupling Between Differential LVPECL, LVDS, HSTL, and …

www.ti.comApplication Report SCAA059C–March 2003–Revised October 2007 AC-Coupling Between Differential LVPECL, LVDS, HSTL, and CML Kal Mustafa/Chris Sterzik.....

Interfacing Between LVPECL, VML, CML and LVDS …

www.ti.comApplication Report SLLA120 - December 2002 1 Interfacing Between LVPECL, VML, CML, and LVDS Levels Nick Holland Serial Gigabit Solutions ABSTRACT This application report introduces the various interface standards used today in modern

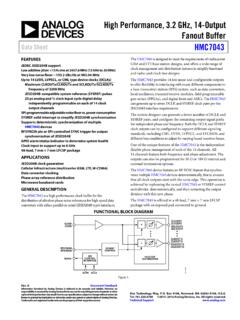

High Performance, 3.2 GHz, 14-Output Fanout Buffer Data ...

www.analog.comHigh Performance, 3.2 GHz, 14-Output Fanout Buffer Data Sheet HMC7043 Rev. B Document Feedback ... LVDS, LVPECL, and LVCMOS, and different bias conditions to adjust for varying board insertion losses. One of the unique features of the HMC7043 is the independent flexible phase management of each of the 14 channels. All

Si5341/40 Rev D Data Sheet

www.skyworksinc.comLow-Jitter, 10 or 4-Output, Any-Frequency, Any-Output Clock Generator ... LVDS, LVPECL, LVCMOS, CML, and HCSL with programmable signal amplitude • Si5341: 4 input, 10 output, 64-QFN 9x9 mm ... The high-resolution fractional MultiSynth …

High Performance, 3.2 GHz, 14 -Output Jitter Attenuator ...

www.analog.comHigh Performance, 3.2 GHz, 14 -Output Jitter Attenuator with JESD204B Data Sheet HMC7044 Rev. C Document Feedback ... Typical value is given at 25°C with two LVPECL high performance clocks at divide by 2, 2 SYSREF clocks (off) VCC9_OUT. 4. 65 . 500 : mA .

Cyclone III Device Handbook Volume 1. Chapter 1. Cyclone ...

www.intel.comSupports I/O standards such as LVTTL, LVCMOS, SSTL, HSTL, PCI, PCI-X, LVPECL, bus LVDS (BLVDS), LVDS, mini-LVDS, RSDS, and PPDS Supports the multi-value on-chip termination (OCT) calibration feature to eliminate variations over process, voltage, and temperature (PVT)

CDCLVP1102 Two-LVPECL Output, High-Performance Clock …

www.ti.comCDCLVP1102 www.ti.com SCAS884D –AUGUST 2009–REVISED DECEMBER 2015 6 Specifications 6.1 Absolute Maximum Ratings over operating free-air …

CDCLVP1208 Eight-LVPECL Output, High-Performance Clock 2:8 ...

www.ti.comCDCLVP1208 www.ti.com SCAS890E –OCTOBER 2009–REVISED NOVEMBER 2015 Changes from Revision B (August 2011) to Revision C Page • Added data sheet flow and layout to conform with new TI standards.

CDCLVP1204 Four LVPECL Output, High …

www.ti.com13 14 15 16 8 7 6 5 CDCLVP1204 OUTP2 OUTN2 OUTP3 OUTN3 1 2 3 4 12 11 10 9 Thermal Pad (1) V CC V AC_REF INN0 INP0 OUTN1 OUTP1 OUTN0 OUTP0 GND IN_SEL INP1 INN1 ...

Similar queries

Interfacing Between LVPECL, VML, CML, LVPECL, Texas Instruments, Differential LVPECL/LVDS to LVTTL, LVPECL LVTTL, LVTTL, Selectable Inputs, 8 LVPECL Outputs, Fanout Buffer Data Sheet ADCLK948, Analog Devices, AC-Coupling Between Differential LVPECL, LVDS, Holland, High, Output, LVPECL high, Two-LVPECL Output, High-Performance Clock, Eight-LVPECL Output, High-Performance Clock, LVPECL Output, High