Transcription of LECTURE 180 – POWER SUPPLY REJECTION RATIO

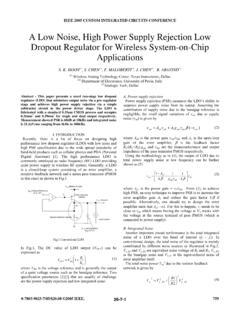

1 LECTURE 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-1 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 LECTURE 180 POWER SUPPLY REJECTION RATIO (READING: GHLM 434-439, AH 286-293)ObjectiveThe objective of this presentation is:1.) Illustrate the calculation of PSRR2.) Examine the PSRR of the two-stage, Miller compensated op ampOutline Definition of PSRR Calculation of PSRR for the two-stage op amp Conceptual reason for PSRR SummaryLecture 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-2 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 What is PSRR?PSRR = Av(Vdd=0)Add(Vin=0) How do you calculate PSRR?You could calculate Av and Add and divide, however+-VDDVSSVddVoutV2V1V2V1Av(V1-V2) AddVddVssVoutFig. 180-02 Vout = AddVdd + Av(V1-V2) = AddVdd - AvVout Vout(1+Av) = AddVdd VoutVdd = Add1+Av AddAv = 1 PSRR+(Good for frequencies up to GB)+ 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-3 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Positive PSRR of the Two-Stage Op AmpM1M2M3M4M5M6M7 VoutVDDVSSVBiasCcCIIVddCIgm1V5rds1gm1 Voutrds2gm6(V1-Vdd)gm2V5rds5gm31I3rds4I3 rds6 Voutrds7 CICcCII+-V1+-VddVddI3gm3-Fig.

2 180-03+V5-gm1 Voutrds2gm6(V1-Vdd)rds4rds6 Voutrds7 CICcCII+-V1+-Vdd-gds1 Vdd-V5 0 The nodal equations are:(gds1 + gds4)Vdd = (gds2 + gds4 + sCc + sCI)V1 (gm1 + sCc)Vout(gm6 + gds6)Vdd = (gm6 sCc)V1 + (gds6 + gds7 + sCc + sCII)VoutUsing the generic notation the nodal equations are:GIVdd = (GI + sCc + sCI)V1 (gmI + sCc)Vout(gmII + gds6)Vdd = (gmII sCc)V1 + (GII + sCc + sCII)VoutwhereGI = gds1 + gds4 = gds2 + gds4, GII = gds6 + gds7, gmI = gm1 = gm2 and gmII = gm6 LECTURE 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-4 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Positive PSRR of the Two-Stage Op Amp - ContinuedUsing Cramers rule to solve for the transfer function,Vout/Vdd, and inverting the transferfunction gives the following = s2[CcCI+CICII + CIICc]+ s[GI(Cc+CII) + GII(Cc+CI) + Cc(gmII gmI)] + GIGII+gmIgmIIs[Cc(gmII+GI+gds6) + CI(gmII + gds6)] + GIgds6We may solve for the approximate roots of numerator asPSRR+ = VddVout gmIgmIIGIgds6 sCcgmI + 1 s(CcCI+CICII+CcCII)

3 GmII Cc + 1 sgmIICcGIgds6 + 1where gmII > gmI and that all transconductances are larger than the channelconductances. PSRR+ = VddVout = gmIgmIIGIgds6 sCcgmI + 1 sCIIgmII + 1sgmIICcGIgds6 + 1 = GIIA vogds6 sGB + 1 s|p2| + 1 sGIIA vogds6GB + 1 LECTURE 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-5 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Positive PSRR of the Two-Stage Op Amp - Continued|PSRR+(j )| dBGIIAv00gds6 GBGIIAv0GB|p2| Fig. 180-04gds6At approximately the dominant pole, the PSRR falls off with a -20dB/decade slope anddegrades the higher frequency PSRR + of the two-stage op the values of Example we get:PSRR+(0) = ,z1 = -5 MHz, z2 = -15 MHzandp1 = -906 HzLecture 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-6 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Concept of the PSRR+ for the Two-Stage Op AmpM1M2M3M4M5M6M7 VoutVDDVSSVBiasCcCIIVddCIFig.

4 180-05 CcVddRoutVoutOther sourcesof PSRR+ besides Cc1 RoutCc VoutVdd0dB1.) The M7 current sink causes VSG6 to act like a ) Therefore, Vdd couples from the source to gate of ) The path to the output is through any capacitance from gate to drain of :The Miller capacitor Cc couples the positive POWER SUPPLY ripple directly to the reduce or eliminate 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-7 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Negative PSRR of the Two-Stage Op Amp withVBias GroundedM1M2M3M4M5M6M7 VoutVDDVSSVBiasCcCIIVssCIFig. 180-06 gmIVoutRICIgmIIV1 CIIRIIgm7 Vss+-VoutCcVBias groundedNodal equations for VBias grounded:0 = (GI + sCc+sCI)V1 - (gmI+sCc)Vogm7 Vss = (gMII-sCc)V1 + (GII+sCc+sCII)VoSolving for Vout/Vss and inverting gives VssVout = s2[CcCI+CICII+CIICc]+s[GI(Cc+CII)+GII(Cc +CI)+Cc(gmII gmI)]+GIGII+gmIgmII[s(Cc+CI)+GI]gm7 LECTURE 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-8 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Negative PSRR of the Two-Stage Op Amp withVBias Grounded - ContinuedAgain using techniques described previously, we may solve for the approximate roots asPSRR- = VssVout gmIgmIIGIgm7 sCcgmI + 1 s(CcCI+CICII+CcCII)gmII Cc + 1 s(Cc+CI)GI + 1 This equation can be rewritten approximately asPSRR- = VssVout gmIgmIIGIgm7 sCcgmI + 1 sCIIgmII + 1 sCcGI + 1 = GIIAv0gm7 sGB + 1 s|p2| +1 sGB gmIGI +1 Comments.

5 PSRR- zeros = PSRR + zerosDC gain Second-stage gain, PSRR- pole (Second-stage gain) x (PSRR+ pole)Assuming the values of Ex. gives a gain of dB and a pole -147 kHz. The dcvalue of PSRR- is very poor for this case, however, this case can be avoided by correctlyimplementing VBias which we consider 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-9 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Negative PSRR of the Two-Stage Op Amp withVBias Connected to VSSM1M2M3M4M5M6M7 VoutVDDVSSVBiasCcCIIVssCIFig. 180-07 rds5rds6 Voutrds7 CICcCgd7+-V1+-VssgmIVoutgmIIV1 RIVBias connected to VSSCIIIf the value of VBias is independent of Vss, then the model shown results. The nodalequations for this model are0 = (GI + sCc + sCI)V1 - (gmI + sCc)Voutand(gds7 + sCgd7)Vss = (gmII - sCc)V1 + (GII + sCc + sCII + sCgd7)VoutAgain, solving for Vout/Vss and inverting givesVssVout = s2[CcCI+CICII+CIICc+CICgd7+CcCgd7]+s[GI( Cc+CII+Cgd7)+GII(Cc+CI)+Cc(gmII gmI)]+GIGII+gmIgmII(sCgd7+gds7)(s(CI+Cc) +GI) LECTURE 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-10 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Negative PSRR of the Two-Stage Op Amp withVBias Connected to VSS - ContinuedAssuming that gmII > gmI and solving for the approximate roots of both the numeratorand denominator givesPSRR- = VssVout gmIgmIIGIgds7 sCcgmI + 1 s(CcCI+CICII+CcCII)gmII Cc + 1 sCgd7gds7 +1 s(CI+Cc)

6 GI + 1 This equation can be rewritten as PSRR- = VssVout GIIAv0gds7 sGB + 1 s|p2| +1 sCgd7gds7 +1 sCcGI + 1 Comments: DC gain has been increased by the RATIO of GII to gds7 Two poles instead of one, however the pole at -gds7/Cgd7 is large and can be the values of Ex. and assume that Cds7 = 10fF, gives,PSRR-(0) = at and -149 MHzLecture 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-11 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Frequency Response of the Negative PSRR of the Two-Stage Op Amp with VBiasConnected to VSS |PSRR-(j )| dBGIIAv00GB|p2| Fig. 180-08gds7 GICcInvalidregion of analysisLecture 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-12 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Approximate Model for Negative PSRR with VBias Connected to GroundM1M2M3M4M5M6M7 VoutVDDVSSVBiasCcCIIVssCIFig.

7 180-09 VBias groundedVSSVssVBiasissM5 or M7 Path through the input stage is not importantas long as the CMRR is through the output stage:vout issZout = gm7 ZoutVss VoutVss = gm7 Zout = gm7 Rout 1sRoutCout+1 Vss20 to40dBVout0dBRoutCout1 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-13 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 Approximate Model for Negative PSRR with VBias Connected to VSSWhat is Zout? Zout = VtIt It = gmIIV1 = gmII gmIVtGI+sCI+sCc Thus, Zout = GI+s(CI+Cc)gmIgMII VssVout = 1+ rds7 Zout1 = s(Cc+CI) + GI+gmIgmIIrds7s(Cc+CI) + GI Pole at -GICc+CI M1M2M3M4M5M6M7 VoutVDDVSSVBiasCcCIIVssCIFig. 180-11 VBias connected to VSSrds7voutZoutVssrds7 Path through Cgd7is ||rds7 VoutCICc+-V1+-gmIVoutgmIIV1 RICII+Cgd7 ItLecture 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-14 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 The two-stage op amp will never have good PSRR because of the Miller 180 POWER SUPPLY REJECTION RATIO (2/16/02)Page 180-15 ECE 6412 - Analog Integrated Circuit Design - II Allen - 2002 SUMMARY PSRR is a measure of the influence of POWER SUPPLY ripple on the op amp outputvoltage PSRR can be calculated by putting the op amp in the unity-gain configuration with theinput shorted.

8 The Miller compensation capacitor allows the POWER SUPPLY ripple at the output to belarge The two-stage op amp will never have good PSRR unless some modifications are made.