PlanetAnalog.com - Power Supply Ripple Rejection and Linear R

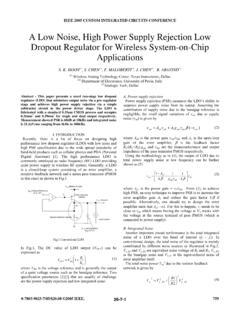

Power supply ripple rejection (PSRR) performance of LDOs ... The worst-case PSRR under worst-case conditions (low supply voltage and high load current) occurs at 10 MHz and the circuit suppresses this noise by 46 dB, as shown in Figure 4 where a 200 mV, 10 MHz pulse is attenuated to 1 mV.

Tags:

Information

Domain:

Source:

Link to this page:

Related search queries

High power supply rejection, Dropout Regulator for Wireless System, Power, High Power Supply Rejection Low Dropout Regulator for Wireless System, Supply, CMOS BANDGAP REFERENCE WITH, Iscas05 high, Power supply, Power Supply Rejection, High supply, Rejection, High, Supply rejection, High power-supply rejection, High Power-Supply-Rejection (PSR) Current-Mode, Drop-Out (LDO) Linear Regulators: Design, IEEE TRANSACTIONS ON MICROWAVE THEORY