Search results with tag "Cmos"

LMC660 CMOS Quad Operational Amplifier datasheet (Rev. D)

www.ti.comSS = 375 μA/Amplifier; Independent of V+ Silicon-GateCMOS process. • Low Distortion: 0.01% at 10 kHz • Slew Rate: 1.1 V/μs See the LMC662 datasheet for a dual CMOS operational amplifier with these same features. APPLICATIONS • High-ImpedanceBuffer or Preamplifier • Precision Current-to-VoltageConverter • Long-TermIntegrator

A D C CMOS Logic Design Solution B F A B D A D

cseweb.ucsd.eduCMOS Logic Design Solution 1. Please draw the minimum CMOS transistor network that implements the functionality of Boolean equation F= ((A+B) C + D)'.

Design and Simulation of CMOS Schmitt Trigger

ijiset.comof Schmitt trigger is using CMOS technology in different foundry. Then, post-layout simulation of Schmitt trigger is done in Microwind 3.1 using90nm, 65nm and 45 nm CMOS technology. The design is implemented using DSCH software to calculate area and power consumption.

Latch-Up White Paper - Analog

www.ti.comCMOS and BiCMOS circuits use NMOS and PMOS transistors to create the circuit functions. In the design of the CMOS integrated circuit, the proximity of the ... There are efforts underway on the JEDEC Latch-Up team to add analog methodology, which will likely be completed late in …

RDA5807M datasheet v1.8

datasheet.lcsc.comVIL CMOS Low Level Input Voltage 0 0.3*VDD V VIH CMOS High Level Input Voltage 0.7*VDD VDD V VTH CMOS Threshold Voltage 0.5*VDD V Table 3-2 DC Electrical Specification (Absolute Maximum Ratings): SYMBOL DESCRIPTION MIN TYP MAX UNIT Tamb Ambient Temperature -40 +90 °C IIN Input Current (1) -10 +10 mA

LMC662 CMOS Dual Operational Amplifier datasheet (Rev. C)

www.ti.comLMC662 www.ti.com SNOSC51C – APRIL 1998– REVISED MARCH 2013 LMC662 CMOS Dual Operational Amplifier Check for Samples: LMC662 1FEATURES DESCRIPTION The LMC662 CMOS Dual operational amplifier is 2• Rail-to-RailOutput Swing ideal for operation from a single supply. It operates

Logic Guide (Rev. AB) - Texas Instruments

www.ti.comthe latest advanced-CMOS families. TI offers process technologies with the ... technology families that are available and ... Power Down) Schmitt Triggers Overvoltage- tolerant Inputs Power-off Output Disable Power-up 3-State Bipolar CMOS BiCMOS AUC 0.8, 1.8, ...

ORCA-Flash4.0 V3 Digital CMOS camera C13440-20CU …

www.hamamatsu.comother scientific CMOS image sensor. Moreover, this value is the performance for high-speed readout of 100 frames/ second at 4 megapixels, which cannot be achieved by the old generation CMOS image sensor. The noise can be reduced further by using the slow scan mode lowering the readout noise to 0.8 electrons (median) or 1.4 electrons (rms).

ORCA-Flash4.0 V3 Digital CMOS camera C13440-20CU …

www.hamamatsu.comother scientific CMOS image sensor. Moreover, this value is the performance for high-speed readout of 100 frames/ second at 4 megapixels, which cannot be achieved by the old generation CMOS image sensor. The noise can be reduced further by using the slow scan mode lowering the readout noise to 0.8 electrons (median) or 1.4 electrons (rms).

An Overview of LVDS Technology - Texas Instruments

www.ti.comthe DS90C031 (LVDS 5V Quad CMOS Differential Line Driver) and the DS90C032 (LVDS 5V Quad CMOS Differen-tial Line Receiver) will be used to illustrate the key points. Over 50 LVDS devices are offered currently (1998) from Na-tional, please refer to the LVDS device datasheets for com-plete specifications. STANDARDS OVERVIEW

LDMOS Technology for RF Power Amplifiers

www.ampleon.comFigure 1: Schematic image of an LDMOS device. Modern LDMOS technology is processed in a CMOS-fab, exploiting 8-in wafer manufacturing and lithography tools with capabilities down to 0.14 μm. Additions to the CMOS process are a source sinker to the substrate, backside metallization, and tungsten shields between the drain and gate. The back-

TL7660 CMOS VOLTAGE CONVERTER - TI.com

www.ti.comwww .ti.com Electrical Characteristics Electrical Characteristics TL7660 CMOS VOLTAGE CONVERTER SCAS794– JUNE 2006 VCC = 5 V, COSC = 0, LV = Open, TA = 25°C (unless otherwise noted) (see Figure 1) PARAMETER TEST …

Project Report A 5.2 GHz Differential Cascode Low Noise ...

images.template.netprocess the minimum length of the transistor’s emitter is 2.5 µm and during the layout process 4 levels of metal are available. A bipolar process was chosen over CMOS since BJTs have improved noise and speed performance. As well, the models for CMOS at radio frequencies are not clearly defined and therefore tend to cause design to be more

6. CMOS Comparators - Università degli Studi di Pavia

ims.unipv.itAnalog Integrated Circuit Design 6. CMOS Comparators 2 Sensitivity is the minimum input voltage that produces a consistent output. The output peak-to-peak swing is in the range of 3-5 V. Therefore, for low speed, in order to detect

CD4069UB CMOS hex inverter - Texas Instruments

www.ti.comCD4069UB CMOS hex inverter 1 1 Features 1• Standardized symmetrical output characteristics • Medium speed operation: tPHL, tPLH = 30 ns at 10 V (Typical) • 100% Tested for quiescent current at 20 V • Maximum input current of 1 µA at 18 V over full package-temperature range, 100 nA at 18 V and 25°C • Meets all requirements of JEDEC ...

Status of the CMOS Image Sensor Industry 2021 - i-Micronews

s3.i-micronews.comCMOS image sensor - competitive landscape CIS and LOGIC foundries capacity Glossary 2 Companies cited in this report 5 Report methodology & definitions 7 What we got right, what we got wrong 9 Executive Summary 14 Context 32 o Global Semiconductor market o Huawei ban timeline o Semiconductor shortages o History of tripple disruption in ...

1/2.9’’ FHD CMOS Image Sensor Data Sheet - WhyCan

whycan.comGC2053 is a high quality 1080P CMOS image sensor, for security camera products, digital camera products and mobile phone camera applications. GC2053 incorporates a 1920H x 1080V pixel array, on-chip 10-bit ADC, and image signal processor. The full scale integration of high-performance and low-power functions makes

CD4066B CMOS Quad Bilateral Switch datasheet (Rev. H)

www.ti.comCD4066B CMOS Quad Bilateral Switch 1 1 Features 1• 15-V Digital or ±7.5-V Peak-to-Peak Switching • 125-ΩTypical On-State Resistance for 15-V Operation • Switch On-State Resistance Matched to Within 5 ΩOver 15-V Signal-Input Range • On-State Resistance Flat Over Full

1/3 4Mega CMOS Image Sensor Datasheet

www.aelnet.co.jpGC4653 is a high quality 4Mega CMOS image sensor, for security camera products, digital camera products and mobile phone camera applications. The full-scale integration of high-performance makes the GC4653 fit the design and reduce the implementation process. GC4653 incorporates a 2560H x 1440V pixel array, on-chip 12/10-bit ADC,

Frost & Sullivan Recognizes Newsight Imaging with the 2022 …

www.semiconductorpackagingnews.comNewsight Imaging specializes in developing high-performance complementary metal-oxide-semiconductor (CMOS) image sensors for three-dimensional (3D) machine vision systems and ... Newsight Imaging (www.nstimg.com) is a leading developer and supplier of advanced CMOS image sensor chips for 3D machine vision and spectral analysis. Newsight’s ...

Jon Fauer, ASC July 2016 Issue 76 Art, Technique, and ...

www.fdtimes.compixel (4096 x 2160) CMOS image sensor that records to internal CompactFlash cards and simultaneously outputs uncompressed RAW. RAW Data was recorded onto a Codex Onboard S Plus re-corder. The Canon EOS-1D C Digital SLR camera has a 5208 x 3477 pixel CMOS sensor for Full Frame Stills, and also shoots motion JPEG compressed 4K video (4096 x 2160).

ADM3202/ADM3222/ADM1385: ローパワー、+3.3 V、RS …

www.analog.comeia/tia-232出力 r1out r2out r1 in r2in eia/tia-232入力* cmos入力 cmos出力 adm1385 gnd t1 t2 dd sd + *各rs-232入力上に5kΩのプルダウン抵抗を内蔵 +3.3v→+6.6v 電圧昇圧器 +6.6v→-6.6v 電圧インバータ *各rs-232入力上に5kΩのプルダウン抵抗を内蔵 +3.3v→+6.6v 電圧昇圧器 …

Manufacturing vaccines during cOvid-19 cMOs/cdMOs tO the ...

cdn.syngeneintl.comContract Manufacturing Organizations (CMOs)/ Contract Development and Manufacturing Organizations (CDMOs) are better positioned to bridge the gap between vaccine demand and supply, safely and at speed. Types of vaccines Vaccines are generally classified as follows: COVID-19 vaccines being developed, currently, are based on these platforms.

CD4066B CMOS Quad Bilateral Switch datasheet (Rev. H)

www.ti.comCD4066B CMOS Quad Bilateral Switch 1 1 Features ... The CD4066B device is a quad bilateral switch intended for the transmission or multiplexing of analog or digital signals. It is pin-for-pin compatible ... the end of the datasheet. Bidirectional Signal Transmission Via Digital Control Logic. 2 CD4066B

Random Offset in CMOS IC Design - Designer’s Guide

designers-guide.orgOct 19, 2007 · Random Offset in CMOS IC Design ECEN4827/5827 Analog IC Design October 19, 2007 Art Zirger, National Semiconductor art.zirger@nsc.com 303-845-4024

20 V, 200 mA, Low Noise, CMOS LDO Linear Regulator Data ...

www.analog.comis a CMOS, low dropout (LDO) linear regulator that operates from 2.7 V to 20 V and provides up to 200 mA of output current. This high input voltage LDO is ideal for the regulation of high performance analog and mixed -signal circuits operating …

Dual/Quad Rail-to-Rail Operational Amplifiers OP295/OP495

www.analog.comoperational amplifiers. By using a bipolar front end, lower noise and higher accuracy than those of CMOS designs have been achieved. Both input and output ranges include the negative supply, providing the user with zero-in/zero-out capability. For users of 3.3 V systems such as lithium batteries, the OP295/OP495 are specified for 3 V operation.

Confidential for truly Only - SparkFun Electronics

cdn.sparkfun.comIndividuals and/or organizations are not allowed to re-distribute said information. ... OV5647 color CMOS QSXGA (5 megapixel) image sensor with OmniBSI™ technology proprietary to OmniVision Technologies PRELIMINARY SPECIFICATION version …

Intelligent video security built to simplify investigations

docs.verkada.comIndustry–Leading 10–Year Product Warranty ... 1/2.8” Progressive CMOS f=2.8mm f=2.8–8mm Fixed P–Iris F1.6 F1.3–F2.4 ... Image Sensor IR Range Focal Length Onboard Storage Operating Specs Iris Dimensions Connectivity From 512GB to …

MIPIの規格動向と測定ソリューション

download.tek.comCMOS Image Sensor MIPI D-PHY Mobile Platform Application Processor (Host) DRAM Mass Storage Display Driver IC Camera Driver IC RFIC GPS Bluetooth / FM Microphone Speaker MEMS Battery SLIMBUS BIF DSI NAND CSI-2 DigRF D-PHY LPDDR テクトロニクス・イノベーション・フォーラム2011 CSI = Camera Serial Interface DSI = Display Serial ...

QUICK SCOPE - Mitutoyo

www2.mitutoyo.co.jpEnhanced Image Processing Functions In industry, where the need for high-accuracy non-contact measurement currently increases, high- ... Zoom CMOS color camera Drive method Focus Optical system Image detecting unit Manual all axes ... Sensor Systems

Sample & Hold Circuits - Pennsylvania State University

www.cse.psu.eduRudy van de Plassche, “CMOS Integrated Analog-to-Digital and Digital-to-Analog Converters- 2nd Edition,” Kluwer Academic Publishers, 2003.Kluwer Academic Publishers, 2003. B. Razavi, “Principles of Data Conversion System Design,” IEEE Press, 1995. 3/14/2011 Insoo Kim

NC7WZ07 SIP6 UDFN6 - ON Semiconductor

www.onsemi.comfabricated with advanced CMOS technology to achieve ultra−high speed with high output drive, while maintaining low static power dissipation over a broad VCC operating range. The device is specified to operate over a very broad VCC operating range. The device is specified to operate over the 1.65 V to 5.5 V VCC range. The inputs

NOIP1SN1300A - PYTHON 1.3/0.5/0.3 MegaPixels Global ...

www.onsemi.comParallel CMOS Output • Random Programmable Region of Interest (ROI) Readout • Serial Peripheral Interface (SPI) • Automatic Exposure Control (AEC) • Phase Locked Loop (PLL) • High Dynamic Range (HDR) Modes Possible • Dual Power Supply (3.3 V and 1.8 V) • −40°C to +85°C Operational Temperature Range • 48−pin LCC • Power ...

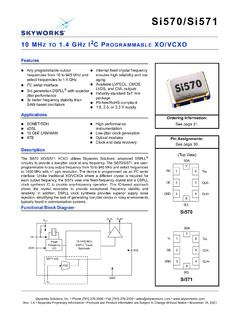

Si570/Si571 Data Sheet - Silicon Labs

www.skyworksinc.comAvailable LVPECL, CMOS, LVDS, and CML outputs Industry-standard 5x7 mm package Pb-free/RoHS-compliant 1.8, 2.5, or 3.3 V supply SONET/SDH xDSL 10 GbE LAN/WAN ATE High performance instrumentation Low-jitter clock generation Optical modules Clock and data recovery Fixed Frequency XO 10-1400 MHz DSPLL Clock Synthesis CLK- CLK+ SCL

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 44, NO. 11 ...

ssl.kaist.ac.krswitch introduces new fault-tolerant protocol to eliminate the routing table and reduces power consumption by 70% compared with the conventionalswitch usingtorus topology. The transceiver with the switch and the RC are implemented in 0.25- m 1P5M CMOS process technology, occupying 2.0 mm and 0.8 mm area, respectively.

Jessica Clements English 626: Postmodernism, Rhetoric ...

owl.purdue.eduNov 07, 2019 · inner logic. ”3 Science, so the ... 17th edition of CMOS (section 14.34). 3 which accounted for the “unbridled individualism of great thinkers, the great benefactors of humankind, who through their singular efforts and struggles would push reason and civilization willy-nilly to the point of true emancipation. ...

This document contains both information and navigation ...

www2.deloitte.comFor CMOs, strategy and communications have needed to pivot in real-time potentially with dramatically-reduced budgets, both to keep costs down in uncertain economic conditions, and to demonstrate sensitivity to what was going on in their customers’ lives. In our new world, organizations are looking for ways to improve the customer experience, and

ADP1706/ADP1707/ADP1708 Data Sheet (Rev. A) - Analog …

www.analog.comCMOS Linear Regulator Data Sheet ADP1706/ADP1707/ADP1708 Rev. A Document Feedback ... Using an advanced proprietary architecture, they provide high power supply rejection and achieve excellent line and load transient response with a small 4.7 µF ceramic output capacitor.

Low Power HDMI to LVDS Display Bridge Data Sheet ADV7613

www.analog.comFabricated in an advanced CMOS process, the ADV7613 is provided in a 9 mm × 9 mm, 100-ball CSP_BGA, RoHS-compliant package. DETAILED FUNCTIONAL BLOCK DIAGRAM . Figure 2. Detailed Functional Block Diagram . DPLL CEC CONTROLLER 5V DETECT AND HPD CONTROLLER EDID REPEATER CONTROLLER PLL EQUALIZER CONTROL INTERFACE …

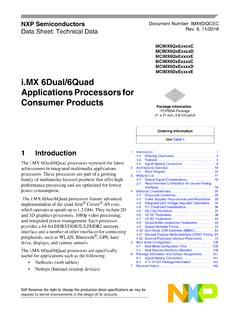

i.MX 6Dual/6Quad Applications Processor Data Sheet for ...

www.nxp.com4.3 Integrated LDO Voltage Regulator Parameters . . 34 ... dual CMOS sensor in terface (parallel or through MIPI ), high-speed USB on-the-go with ... The two characteristics that identify which data sheet a specific part applies to are the part number series field and the temperature grade (junction) field: ...

Inspiron 3585 Setup and Specifications - Dell

dl.dell.comHard drive One 2.5-inch hard drive, SATA 3 ... Sensor type CMOS sensor technology Resolution: Still image 0.92 megapixel Video 1280 x 720 (HD) at 30 fps 14 Specifications of Inspiron 3585. Keyboard shortcuts. Table 14. Camera specifications .

DH-IPC-HFW2439S-SA-LED-S2 - Dahuasecurity.com

www.dahuasecurity.comwww.dahuasecurity.com DH-IPC-HFW2439S-SA-LED-S2 4MP Lite Full-color Fixed-focal Bullet Network Camera · 4MP, 1/3" CMOS image sensor, low illuminance, high image definition · Outputs 4MP (2560 × 1440) @ 25/30 fps, Max. supports 4MP (2688 × 1520) @ 20 fps · H.265 codec, high compression rate, ultra-low bit rate · Built-in warm lights, max. illumination …

MIPI/DSI Receiver with HDMI Transmitter Data Sheet ADV7533

www.analog.comOne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. ... 5 V tolerant I 2C and HPD I/Os, no extra device needed No audio master clock needed for supporting S/PDIF ... Fabricated in an advanced CMOS process, the ADV7533 is available in a space saving, 49-ball, WLCSP surface mount

Area of Online Internship for the Undergraduate Students

www.iiti.ac.in2. Silicon Photonics; Integrated CMOS Photonics 3. Microwave & RF Photonics, Optical Antenna 4. Devices for Optical Communication & Interconnects 5. Nano-scale devices for Advanced Memory and Computing 6. Nanoelectronics, VLSI Technology & Device Fabrication School of Humanities and Social Sciences Dr. Kalandi Charan Pradhan 1.

INSTRUCTION MANUAL INSTRUCTION MANUAL

gdlp01.c-wss.comThe EOS 40D is a high-performance, digital SLR camera featuring a fine-detail CMOS sensor with 10.10 effective megapixels, DIGIC III, high-precision and high-speed 9-point AF (all cross-type points), and high-speed 6.5 fps continuous shooting. The camera is …

Layout of Analog CMOS Integrated Circuit

ims.unipv.itA resistor is made of a strip of resistive layer. The endings resistance can be significant! R W L ... Place resistors away from power devices Use electrostatic shielding Use proper endings. F ... Finger two or more resistors for matching Do not snake a resistor; use metal to make turns Well under the resistor to shield from interference ...

CMOS Operational Amplifier Design

www2.eecs.berkeley.eduA two stage compensated differential amplifier with self biased Cascode circuitry was designed in 130nm CMOS technology which achieved low power operation of 1.9mW with modern supply voltage of 1.2v, and fast 0.1% settling time of less than 4.9ns for load capacitance of 5pF, with

Similar queries

CMOS, Operational Amplifier, Amplifier, LMC662, Dual CMOS operational amplifier, CMOS Logic Design Solution, Design, Analog, Circuits, Analog methodology, LMC662 CMOS Dual operational amplifier, LMC662 www.ti.com, Logic Guide, Texas Instruments, Advanced, Technology, Tolerant, CMOS image, An Overview of LVDS Technology, Quad CMOS, Line, Quad CMOS Differen-tial Line Receiver, LDMOS Technology for RF Power Amplifiers, Image, TL7660 CMOS, Www .ti.com, Characteristics, Characteristics TL7660 CMOS, Transistor, 6. CMOS Comparators, Inverter, CMOS image sensor, FHD CMOS Image Sensor, Digital, CD4066B CMOS Quad Bilateral Switch datasheet, CD4066B CMOS Quad Bilateral Switch, Switch, 4Mega CMOS Image Sensor Datasheet, High, Performance, Performance complementary metal-oxide-semiconductor, CMOS sensor, Organizations CMOs, Organizations, CD4066B, Quad bilateral switch, Datasheet, CMOS LDO, Regulator, Operational, Confidential for truly Only, Industry, Image Sensor, Sensor, Sample & Hold Circuits, Advanced CMOS, Phase Locked Loop, Logic, Series, Inspiron 3585, Inch, VLSI, Layout of Analog CMOS Integrated Circuit, Strip, Resistors, Power, Metal, CMOS Operational Amplifier Design, Low power