Search results with tag "Locked"

The Delay-Locked Loop - University of California, Los Angeles

www.seas.ucla.eduDelay-locked loops (DLLs) can be considered as feedback circuits that phase lock an output to an input without the use of an oscillator. In some applications, DLLs are neces-sary or preferable over phase-locked loops (PLLs), with their advantages including lower sensitivity to supply noise and lower phase noise. This

JESUS APPEARS TO THE DISCIPLES BEHIND LOCKED DOORS …

anchorss.orgJESUS APPEARS TO THE DISCIPLES BEHIND LOCKED DOORS / 20:19-23 / 244. Mary's announcement ... with the doors locked for fear of the Jews, Jesus came and stood among them. ... behind closed doors, but he will not unlock them for us. Unless we step out of our hiding places, we will never see all that ...

The Rights of Land-Locked States Under the International ...

unohrlls.org28 Endalcachew Bayeh: The Rights of Land-Locked States Under the International Law: The Role of Bilateral/Multilateral Agreements world are land-locked states (Uprety, 2003).

Phase-Locked Loop Design Fundamentals - NXP

www.nxp.comPhase-Locked Loop Design Fundamentals Application Note, Rev. 1.0 2 Freescale Semiconductor with the reader. Since the scope of this article is practical in nature all theoretical derivations have been omitted, hoping to simplify and clarify the content. A bibliography is included for those who desire to pursue the theoretical aspect.

CD4046B Phase-Locked Loop: A Versatile Building Block for ...

www.ti.com6 CD4046B Phase-Locked Loop: A Versatile Building Block for Micropower Digital and Analog Applications Phase comparator I is an exclusive-OR network that operates analogously to an overdriven balanced mixer. To maximize the lock range, the signal- and comparator-input frequencies must have 50% duty cycle.

Case report: Acute locked thoracic spine: treatment with a ...

www.iaopt.orgCasereport Acutelockedthoracicspine:treatmentwithamodifiedSNAG S.J.Horton SchoolofPhysiotherapy,UniversityofOtago,Dunedin,NewZealand INTRODUCTION

WELCOME TO THE NEXT GENERATION OF SISSY ... - Locked …

lockedinlace.comDigitally Locked via Portable Device or Server Un-relenting Remote Controlled via Proprietary Software Un-breakable Shemale Sheath with Electrodes for Pleasure and Pain Training Un-forgiving Flexi-Rear for Easy Access Un-believable Waterproof Allowing Bathing and Urination Un-pickable Low Waist and Smooth Front

Phase Locked Loops (PLL) and Frequency Synthesis

rfic.eecs.berkeley.eduPhase Locked Loops A PLL is a truly mixed-signal circuit, involving the co-design of RF, digital, and analog building blocks. A non-linear negative feedback loop that locks the phase of a VCO to a reference signal. Applications include generating a clean, tunable, and stable reference (LO) frequency, a process referred to as frequency synthesis

MT-086: Fundamentals of Phase Locked Loops (PLLs)

www.analog.comA phase-locked loop is a feedback system combining a voltage controlled oscillator (VCO) and a ... counter element to bring the very high input frequency down to a range at which standard CMOS will operate. This counter, called a prescaler, is shown in Figure 3B.

Charter of Economic Rights and Duties of States

www.aaas.orgInternational Economic Order, which underlined the vital importance of the Charter to be adopted by the ... Free access to and from the sea by land-locked countries within the framework of the above principles. Chapter II Economic rights and duties of states ... it shall be settled under the domestic law of the nationalizing State and by its ...

Wideband Synthesizer with Integrated VCO Data Sheet ADF4350

www.analog.cominteger-N phase-locked loop (PLL) frequency synthesizers if used with an external loop filter and external reference frequency. The . ADF4350 has an integrated voltage controlled oscillator (VCO) with a fundamental output frequency ranging from 2200 MHz to 4400 MHz. In addition, divide-by-1/2/4/8 or 16

International Securities - CommSec

www.commsec.com.auINTERNATIONAL SECURITIES TRADING APPLICATION FORM MKTG1008 (09/20) 1 of 2 ... LOCKED BAG 22 AUSTRALIA SQUARE NSW 1215 ... Please note that you have an obligation under US tax laws to provide information necessary for US tax withholding and reporting requirements. The information on this form has been provided to assist you with your …

ECEN720: High-Speed Links Circuits and Systems Spring 2021

people.engr.tamu.edu• Delay-Locked Loop (DLL) locally generates the multiple clock phases for the phase interpolators • DLL can be per-channel or shared by a small number (4) • Same architecture can be used in a forwarded-clock system • Replace frequency synthesis PLL with forwarded-clock signals 29

Fractional/Integer-N PLL Basics - Texas Instruments

www.ti.comFractional/Integer-N PLL Basics Edited by Curtis Barrett Wireless Communication Business Unit Abstract Phase Locked Loop (PLL) is a fundamental part of radio, wireless and telecommunication technology. The goal of this document is to review the theory, design and analysis of PLL circuits.

25 MHz to 3000 MHz Fractional-N PLL with Integrated VCO ...

www.analog.comtional-N, phase-locked loop (PLL) that features an integrated voltage controlled oscillator (VCO) with a fundamental frequency of 1500 MHz to 3000 MHz and an integrated VCO output divider (divide by 1, 2, 4, 6, … 62) that enables the HMC832A to generate continuous frequencies from 25 MHz to 3000 MHz. The integrated phase detector (PD) and Σ-Δ

Intercessions for use during the pandemic

www.scotland.anglican.orgThe doors of the house where the disciples had met were locked (John 20. 19) Ever-present God, be with us in our isolation, be close to us in our distancing, be healing in our sickness, be joy in our sadness, be light in our darkness, be wisdom in our confusion, be all that is familiar when all is unfamiliar, that when the doors reopen

Human Trafficking and Child Welfare: A Guide for Child ...

www.childwelfare.govlocked up to be a victim. Reality: While some victims may be physically held by their trafficker, psychological means of control (e.g., trauma bonds, threats, coercion) are far more common. For more information about how States classify human trafficking, view Information Gateway’s . Definitions of Human Trafficking. at . https://www.

Integrated, Quad RF Transceiver with Observation Path …

www.analog.comsuch as analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and general-purpose input/outputs (GPIOs) that provide an array of digital control options are also integrated. To achieve a high level of RF performance, the transceiver includes five fully integrated phase-locked loops (PLLs). Two

MT-008: Converting Oscillator Phase Noise to Time Jitter

www.analog.comthe graph relevant to modern ADC applications, the oscillator frequency (sampling frequency) is ... An alternative solution is to use a phase-locked-loop (PLL) in conjunction with a voltage-controlled oscillator to "clean up" a noisy system clock as shown in Figure 8. There are many good references on PLL design (see References 10-13, for example),

Near-Single Sideband Modulation in Strong Optical ...

nanophotonics.eecs.berkeley.eduNear-Single Sideband Modulation in Strong Optical Injection-Locked Semiconductor Lasers Hyuk-Kee Sung, Erwin K. Lau and Ming C. Wu Department of …

Digital Phase Locked Loop Induction Motor Speed …

lejpt.academicdirect.orgLeonardo Electronic Journal of Practices and Technologies ISSN 1583-1078 Issue 20, January-June 2012 p. 159-174 161 generates the slip frequency command through a controller and a limiter.

Phase Locked Loop Circuits - UC Santa Barbara

web.ece.ucsb.eduphase or frequency can be used as the input or output variables. Of course, phase and frequency are interrelated by: Phase detector Loop filter VCO φin(t) ωin(t) φout(t) ωout(t) ve(t) Vcont out φ =φ +∫ω φ ω = t t t dt dt d t 0 ( ) (0) ( ') ' ( ) Applications: There are many applications for the PLL, but we will study: a. Clock ...

Quality factor, Q

web.ece.ucsb.educommunication system. While many applications use a phase locked loop technique to correct for frequency drift, it is good practice to build oscillators with some attempt to minimize such drift by selecting appropriate components. Inductors and capacitors often drift in value with temperature. Permeability of core

RFM69HCW - SparkFun Electronics

cdn.sparkfun.comPLL Phase-Locked Loop FCC Federal Communications Commission POR Power On Reset Fdev Frequency Deviation RBW Resolution BandWidth FIFO First In First Out RF Radio Frequency FIR Finite Impulse Response RSSI Received Signal Strength Indicator FS Frequency Synthesizer Rx Receiver FSK Frequency Shift Keying SAW Surface Acoustic Wave

Microwave Wideband Synthesizer with Integrated VCO Data ...

www.analog.cominteger-N phase-locked loop (PLL) frequency synthesizers when used with an external loop filter and an external reference frequency. The wideband microwave VCO design permits frequency operation from 6.8 GHz to 13.6 GHz at one radio frequency (RF) output. A series of frequency dividers at another

Motortronics VMX Series Compact Soft Starter User Manual

files.valinonline.com"When an induction motor is operated at any service factor greater than 1.0, it may have efficiency, power factor and speed different than those at rated load. Locked rotor torque and current and breakdown torque will remain the same. A motor operating continuously at any service factor greater than

The Biquadratic Filter - University of California, Los Angeles

www.seas.ucla.edution, as practiced in type II phase-locked loops, or 2) we can make one of the integrators lossy, e.g., we can change ks 1/ to ks 1/( +a). The latter is realized if a fraction of the integrator’s output is returned to its input without phase shift. Illustrated in Figure 3(a), such an arrangement yields . A B s sk k 1 1 a = + (8)

RF Agile Transceiver Data Sheet AD9364 - Analog Devices

www.analog.comThe fully integrated phase-locked loops (PLLs) provide low power fractional-N frequency synthesis for all Rx and Tx channels. All VCO and loop filter components are integrated. The core of the AD9364 can be powered directly from a 1.3 V regulator. The IC is controlled via a standard 4-wire serial port and four real-time input control pins.

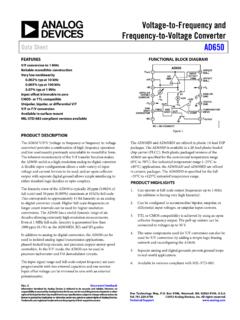

Voltage-to-Frequency and Frequency-to-Voltage Converter ...

www.analog.comused in isolated analog signal transmission applications, phased-locked loop circuits, and precision stepper motor speed controllers. In the F/V mode, the AD650 can be used in precision tachometer and FM demodulator circuits. The input signal range and full-scale output frequency are user-programmable with two external capacitors and one resistor.

Microwave Wideband Synthesizer with Integrated VCO Data ...

www.analog.comMicrowave radio . GENERAL DESCRIPTION The ADF5610 allows implementation of fractional-N or Integer N phase-locked loop (PLL) frequency synthesizers when used with an external loop filter and an external reference source. The wideband microwave voltage controlled oscillator (VCO) designpermits frequency operation from 7300 MHz to

THE WORLD CLIMATE AND SECURITY REPORT 2021

imccs.orgThe International Military Council on Climate and Security (IMCCS) is a group of senior military leaders, security experts, and ... defense has locked itself into a hydrocarbon-based dependency for many years to come. ... “significant or higher security risks under current circumstances” - importantly, across all regions of the world. On

High Frequency VCO Design and Schematics

www.qsl.netcontained within a phase-locked loop and the frequency of modulation lies within the closed-loop bandwidth, unwanted interactions can result. One of the most serious load pulling situations that can occur in practice arises in modulators where the modulation signal causes (low-frequency) baseband frequency modulation of the load.

EMBEDDED SYSTEMS PROGRAMMING WITH THE PIC16F877

academic.csuohio.eduPLL = Phase-Locked Loop POR = Power-On Reset PROM = Programmable Read Only Memory PSP = Parallel Slave Port PWM = Pulse Width Modulation Q = Flip-Flop, Counter, or Shift Register Output State (Data Out) RAM = Random Access Memory (A Read/Write Memory) RC = Resistor/Capacitor (Time Constant or Circuit)

NOIP1SN1300A - PYTHON 1.3/0.5/0.3 MegaPixels Global ...

www.onsemi.comParallel CMOS Output • Random Programmable Region of Interest (ROI) Readout • Serial Peripheral Interface (SPI) • Automatic Exposure Control (AEC) • Phase Locked Loop (PLL) • High Dynamic Range (HDR) Modes Possible • Dual Power Supply (3.3 V and 1.8 V) • −40°C to +85°C Operational Temperature Range • 48−pin LCC • Power ...

Radiation Tolerant Kintex UltraScale XQRKU060 FPGA Data …

www.xilinx.comThe serial transmitter and receiver are independent circ uits that use an advanced phase-locked loop (PLL) architecture to multiply the reference frequency input by certain programmable numbers between 4 and 25 to become the bit-serial data clock. Each transcei ver has a large number of user-definable features and parameters.

Digital Phase Locked Loop - University of Maine

ece.umaine.edu3.1.2 2 Input NAND Figure 3 shows a common 2 input CMOS nand gate. A 2:1 overall well width ratio (see Inverter) was employed. 3.1.3 3 Input NAND Figure 4 shows a common 3 input CMOS nand gate. A 2:1 overall well width ratio (see Inverter) was employed. 3.1.4 8 Input NAND Figure 5 shows a common 8 input CMOS nand gate.

Lecture 17: Clock Recovery - Stanford University

web.stanford.eduVCO-based Phase Locked Loop • Controlled variable is phase of the output clock • Main difference from DLL is the VCO transfer function: • The extra VCO pole needs to be compensated by a zero in the loop filter: Filter ref clk clk φerr Kpd F(s) KVCO KVCO (Hz/V) KpdF(s) (V/rad) HVCO()s KVCO s = ----- - Fs() Kf()1sz+ ⁄ 1 s

MMCM and PLL Dynamic Reconfiguration Application Note

www.xilinx.comUltraScale™, and UltraScale+™ FPGAs. Similarly, the phase-locked loop (PLL) can be changed through the dynamic reconfiguration port (DRP). An explanation of the behavior of the internal DRP control registers is accompanied by a reference design that uses a state machine to drive

TEA5767HN Low-power FM stereo radio for handheld …

www.sparkfun.comn Phase-locked loop (PLL) synthesizer tuning system n I2C-bus and 3-wire bus, ... Low-power FM stereo radio for handheld applications Rev. 05 — 26 January 2007 Product data sheet. ... PHASEFIL 18 phase detector loop filter PILFIL 19 pilot detector low-pass filter n.c. 20 …

MT9P031 - 1/2.5-Inch 5 Mp CMOS Digital Image Sensor

www.onsemi.comon−chip, phase−locked loop (PLL) to generate all internal clocks from a single master input clock running between 6 and 27 MHz. The maximum pixel rate is 96 Mp/s, corresponding to a clock rate of 96 MHz. Figure 1 illustrates a block diagram of the sensor. Figure 1. Block Diagram Pixel Array 2752H x 2004V SCLK SDATA SADDR PIXCLK DOUT[11:0] LV FV

2021 United States Aviation Climate Action Plan

www.faa.govpandemic locked down cities and states, passenger air travel—both domestic and international—ground to a halt. Although demand for air cargo remained robust, the pandemic had a crippling effect on passenger aviation globally. The year 2020 saw layoffs, bankruptcies, and an unprecedented drop in commercial aviation.

Locked-In Retirement Accounts (LIRAs) - Ontario

www.fsco.gov.on.caretirement savings arrangement, the Locked-in Retirement Account (LIRA). A LIRA is a registered retirement savings plan (RRSP) that meets the requirements set out in Schedule 3 to the Regulation (Schedule 3). The key feature of LIRAs that distinguishes them from regular (non-locked-in) RRSPs is that the

Locked-in RRSPs and Your Options - RBC

contact.rbc.com2 Locked-in RRSPs and Your Options Locked-in RRSPs and Your Options 3 3 > LIFE INCOME FUND (LIF) aND RESTRICTED LIFE INCOME FUND (RLIF) FIGURE 1 HOW LIF/RLIF PAYMENTS ARE CALCULATED Minimum Payment Note: The provinces of British Columbia, Alberta, Manitoba, Ontario, Quebec, Newfoundland & Labrador and Nova Scotia as well as …

Locked Rotor Torques - Bradleys Motors

www.bradleysmotors.comHow To Get The Most From Your Electric Motors Table 2. NEMA Torque Designs For Three-Phase Motors IŒMA Rotor Breakdown Rotor Percent Torqtæ

Similar queries

Delay-Locked Loop, Delay-locked, Phase, Locked, THE DISCIPLES BEHIND LOCKED DOORS, THE DISCIPLES BEHIND LOCKED DOORS / 20, Doors, Closed doors, Locked States Under the International, Locked loop, Applications Phase, Report: Acute locked thoracic spine: treatment, Phase Locked, CMOS, Charter of Economic Rights and Duties, States, International, Under, Loop, Fractional, N PLL, Texas Instruments, Phase Locked Loop, Intercessions for use during the, The disciples, Child Welfare, Quad RF Transceiver with Observation Path, Digital, Locked loops, Applications, Optical, Strong Optical Injection-Locked Semiconductor Lasers, Digital Phase Locked Loop Induction, Microwave, Synthesizer, Phase-locked loop, Motortronics, Induction motor, Motor, The Biquadratic Filter, Analog Devices, The International, Digital Phase Locked Loop, 2 2 Input NAND, 2 input, Nand gate, Input NAND, Input, Design, Locked-in, Locked Rotor Torques, Rotor