Transcription of HRF3205, HRF3205S - redrok.com

1 2001 Fairchild Semiconductor CorporationHRF3205, HRF3205S Rev. BHRF3205, HRF3205S100A, 55V, Ohm, N-Channel, Power MOSFETsThese are N-Channel enhancement mode silicon gate power field effect transistors. They are advanced power MOSFETs designed, tested, and guaranteed to withstand a specified level of energy in the breakdown avalanche mode of operation. All of these power MOSFETs are designed for applications such as switching regulators, switching converters, motor drivers, relay drivers, and drivers for high power bipolar switching transistors requiring high speed and low gate drive power. These types can be operated directly from integrated : Calculated continuous current based on maximum allowable junction temperature. Package limited to 75A continuous, see Figure 100A, 55V (See Note) Low On-Resistance, rDS(ON) = Temperature Compensating PSPICE Model Thermal Impedance SPICE Model UIS Rating Curve Related Literature - TB334, Guidelines for Soldering Surface Mount Components to PC Boards SymbolPackagingJEDEC TO-220 ABJEDEC TO-263 ABOrdering InformationPART NUMBERPACKAGEBRANDHRF3205TO-220 ABHRF3205 hrf3205 STO-263 ABHRF3205 SNOTE: When ordering, use the entire part number.

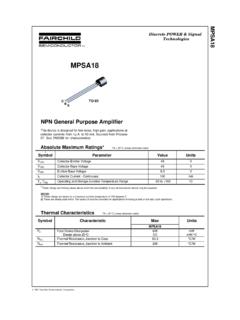

2 Add the suffix T to obtain the TO-263AB variant in tape and reel, , (FLANGE)GATESOURCEDRAIN (FLANGE)Data SheetDecember 2001 2001 Fairchild Semiconductor CorporationHRF3205, HRF3205S Rev. BAbsolute Maximum RatingsTC = 25oC, Unless Othewise SpecifiedDrain to Source Voltage (Note 1) .. VDSS55 VDrain to Gate Voltage (RGS = 20k ) (Note 1) .. VDGR55 VGate to Source Voltage .. VGS 20 VVDrain CurrentContinuous .. IDPulsed Drain Current (Note 2) .. IDM100390 AAPulsed Avalanche Rating .. EASF igure 10 Power Dissipation .. PDDerate Above 25oC .. and Storage Temperature .. TJ, TSTG-55 to 175oCMaximum Temperature for SolderingLeads at ( ) from Case for 10s .. TLPackage Body for 10s, See Techbrief 334 .. Tpkg300260oCoCCAUTION: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device.

3 This is a stress only rating and operation of thedevice at these or any other conditions above those indicated in the operational sections of this specification is not :1. TJ = 25oC to SpecificationsTC = 25oC, Unless Otherwise Specified PARAMETERSYMBOLTEST CONDITIONSMINTYPMAXUNITSD rain to Source Breakdown VoltageBVDSSID = 250 A, VGS = 0V55--VGate to Source Threshold VoltageVGS(TH)VGS = VDS, ID = 250 A2-4 VZero Gate Voltage Drain CurrentIDSSVDS = 55V, VGS = 0V--25 AVDS = 44V, VGS = 0V, TC = 150oC--250 AGate to Source Leakage CurrentIGSSVGS = 20V--100nABreakdown Voltage TemperatureCoefficient V(BR)DSS/ TJReference to 25oC, ID = 250 to Source On ResistancerDS(ON)ID = 59A, VGS = 10V (Figure 4) Turn-On Delay Timetd(ON)VDD = 28V, ID 59A,RL = , VGS = 10V,RGS = -14 - nsRise Timetr-100-nsTurn-Off Delay Timetd(OFF)-43 - nsFall Timetf-70 - nsTotal Gate ChargeQgVDD = 44V, ID 59A,VGS = 10V, Ig(REF) = 3mA(Figure 6)

4 --170nCGate to Source ChargeQgs--32nCGate to Drain Miller ChargeQgd--74nCInput CapacitanceCISSVDS = 25V, VGS = 0V,f = 1 MHz (Figure 5)-4000-pFOutput CapacitanceCOSS-1300-pFReverse Transfer CapacitanceCRSS-480-pFInternal Source InductanceLSMeasured From the Contact Screw on Tab to Center of Die Modified MOSFET Symbol Showing the Internal Devices - nHMeasured From the Drain Lead, 6mm ( ) From Package to Center of DieInternal Drain InductanceLDMeasured From the Source Lead, 6mm ( ) From Head-er to Source Bonding - nHThermal Resistance Junction to CaseR Resistance Junction to AmbientR JATO-220--62oC/WTO-263 (PCB Mount, Steady State)--40oC/WLSLDGDSHRF3205, HRF3205S 2001 Fairchild Semiconductor CorporationHRF3205, HRF3205S Rev. BSource to Drain Diode Specifications PARAMETERSYMBOLTEST CONDITIONSMINTYPMAXUNITSC ontinuous Source to Drain CurrentISDMOSFET Symbol ShowingThe Integral Reverse P-NJunction Diode--100 (Note 1 APulsed Source to Drain Current (Note 2)ISDM--390 ASource to Drain Diode VoltageVSDISD = 59A (Note 4) Recovery TimetrrISD = 59A, dISD/dt = 100A/ s (Note 4)-110170nsReverse Recovered ChargeQRRISD = 59A, dISD/dt = 100A/ s (Note 4)-450680nCNOTE:2.)

5 Repetitive rating; pulse width limited by maximum junction temperature (See Figure 11)Typical Performance Curves FIGURE 1. OUTPUT CHARACTERISTICSFIGURE 2. OUTPUT CHARACTERISTICSFIGURE 3. TRANSFER CHARACTERISTICSFIGURE 4. NORMALIZED DRAIN TO SOURCE ON RESISTANCE vs JUNCTION s PULSE WIDTH TC = 25oCVGS IN DECENDING ORDERVDS, DRAIN TO SOURCE VOLTAGE (V)ID, DRAIN TO SOURCE CURRENT (A) s PULSE WIDTH TC = 175oCVDS, DRAIN TO SOURCE VOLTAGE (V)ID, DRAIN TO SOURCE CURRENT (A) IN DECENDING , GATE TO SOURCE VOLTAGE (V)ID, DRAIN TO SOURCE CURRENT(A)PULSE DURATION = 80 s VDS = 25 VTJ = 25oCTJ = 175oCDUTY CYCLE = = 98A, VGS = 10 VPULSE DURATION = 80 sNORMALIZED DRAIN TO SOURCEON RESISTANCETJ, JUNCTION TEMPERATURE (oC)DUTY CYCLE = MAXHRF3205, HRF3205S 2001 Fairchild Semiconductor CorporationHRF3205, HRF3205S Rev.

6 BFIGURE 5. CAPACITANCE vs DRAIN TO SOURCE VOLTAGEFIGURE 6. GATE CHARGE WAVEFORMS FOR CONSTANTGATE CURRENTFIGURE 7. SOURCE TO DRAIN DIODE FORWARD VOLTAGEFIGURE 8. FORWARD BIAS SAFE OPERATING AREAFIGURE 9. MAXIMUM CONTINUOUS DRAIN CURRENT vs CASE TEMPERATURE FIGURE 10. UNCLAMPED INDUCTIVE SWITCHING CAPABILITYT ypical Performance Curves (Continued)01000200030004000500060007000 800010100 VGS = 0V, f = 1 MHzCISS = CGS + CGDCRSS = CGDCOSS CDS + CGSCISSCOSSCRSSC, CAPACITANCE (pF)VDS, DRAIN TO SOURCE VOLTAGE (V)104812162003672108144180Qg, GATE CHARGE (nC)VGS, GATE TO SOURCE VOLTAGE (V)VDS = 44 VVDS = 28 VVDS = 11 VID = , SOURCE TO DRAIN VOLTAGE (V)ISD, REVERSE DRAIN CURRENT(A)TJ = 175oCTJ = 25oCPULSE DURATION = 80 sDUTY CYCLE = MAX1101001000110100 LIMITED BY rDS(ON)AREA MAY BEOPERATION IN THISVDSS(MAX) = 55 VVDS, DRAIN TO SOURCE VOLTAGE (V)100 s1ms10ms10 sID, DRAIN CURRENT (A)TC, CASE TEMPERATURE (oC)ID, DRAIN CURRENT (A)0306090120255075100125150175BY PACKAGECURRENT , AVALANCHE CURRENT (A)tAV, TIME IN AVALANCHE (ms)tAV = (L)(IAS)/( *RATED BVDSS - VDD)

7 If R = 0If R 0tAV = (L/R)ln[(IAS*R)/( *RATED BVDSS - VDD) +1]STARTING TJ = 25oCSTARTING TJ = , HRF3205S 2001 Fairchild Semiconductor CorporationHRF3205, HRF3205S Rev. BFIGURE 11. NORMALIZED MAXIMUM TRANSIENT THERMAL IMPEDANCETest Circuits and Waveforms FIGURE 12. UNCLAMPED ENERGY TEST CIRCUITFIGURE 13. UNCLAMPED ENERGY WAVEFORMSFIGURE 14. GATE CHARGE TEST CIRCUITFIGURE 15. GATE CHARGE WAVEFORMT ypical Performance Curves (Continued) :DUTY FACTOR: D = t1/t2 PEAK TJ = PDM x Z JC x R JC + TCPDMt1t2t, RECTANGULAR PULSE DURATION (s)SINGLE PULSEZ JC, NORMALIZEDTHERMAL IMPEDANCEDUTY CYCLE - DESCENDING LIAS+-VDSVDDRGDUTVARY tP TO OBTAINREQUIRED PEAK IAS0 VVDDVDSBVDSStPIAStAV0 RLVGS+-VDSVDDDUTIG(REF)Qg(TOT)QgdQgsVDS0 VGSVDDIG(REF)0 hrf3205 , HRF3205S 2001 Fairchild Semiconductor CorporationHRF3205, HRF3205S Rev.

8 BFIGURE 16. SWITCHING TIME TEST CIRCUITFIGURE 17. RESISTIVE SWITCHING WAVEFORMSTest Circuits and Waveforms (Continued)VGSRLRGSDUT+-VDDVDSVGStONtd(O N)tr90%10%VDS90%10%tftd(OFF)tOFF90%50%50 %10%PULSE WIDTHVGS00 hrf3205 , HRF3205S 2001 Fairchild Semiconductor CorporationHRF3205, HRF3205S Rev. BPSPICE Electrical Model SUBCKT HRF3205P3 2 1 3 ;rev 7/25/97CA 12 8 15 14 6 8 7 5 DBODYMODDBREAK 5 11 DBREAKMODDPLCAP 10 5 DPLCAPMODEBREAK 11 7 17 18 57 EDS 14 8 5 8 1 EGS 13 8 6 8 1 ESG 6 10 6 8 1 EVTHRES 6 21 19 8 1 EVTEMP 20 6 18 22 1IT 8 17 1 LDRAIN 2 5 1e-9 LGATE 1 9 3 7 LGATE LSOURCE 16 6 8 8 MMEDMODMSTRO 16 6 8 8 MSTROMODMWEAK 16 21 8 8 MWEAKMODRBREAK 17 18 RBREAKMOD 1 RDRAIN 50 16 RDRAINMOD 9 20 2 5 10 RLGATE 1 9 26 RLSOURCE 3 7 11 RSLC1 5 51 RSLCMOD 1e-6 RSLC2 5 50 1e3 RSOURCE 8 7 RSOURCEMOD 22 8 RVTHRESMOD 1 RVTEMP 18 19 RVTEMPMOD 1S1A 6 12 13 8 S1 AMODS1B 13 12 13 8 S1 BMODS2A 6 15 14 13 S2 AMODS2B 13 15 14 13 S2 BMODVBAT 22 19 DC 1 ESLC 51 50 VALUE={(V(5,51)/ABS(V(5,51)))*(PWR(V(5,5 1)/(1e-6*550),3))}.

9 MODEL DBODYMOD D (IS = RS = TRS1 = TRS2 = 5e-6 CJO = TT = 4e-7 M = ).MODEL DBREAKMOD D (RS = 6 IKF = 30 TRS1 = -3e- 3 TRS2 = 3e-6).MODEL DPLCAPMOD D (CJO = 9IS = 1e-3 0N = 1 M = VJ = ).MODEL MMEDMOD NMOS (VTO = KP = IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u RG = 1).MODEL MSTROMOD NMOS (VTO = KP = 150 IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u).MODEL MWEAKMOD NMOS (VTO = KP = IS = 1e-30 N = 10 TOX = 1 L = 1u W = 1u RG = 10).MODEL RBREAKMOD RES (TC1 = 8e- 4TC2 = 4e-6).MODEL RDRAINMOD RES (TC1 = 8e-2 TC2 = 5e-6).MODEL RSLCMOD RES (TC1 = 1e-4 TC2 = ).MODEL RSOURCEMOD RES (TC1 = 1e-4 TC2 = ).MODEL RVTHRESMOD RES (TC1 = TC2 = ).MODEL RVTEMPMOD RES (TC1 = 3TC2 = -7e-6).MODEL S1 AMOD VSWITCH (RON = 1e-5 ROFF = VON = -9 VOFF= -4).MODEL S1 BMOD VSWITCH (RON = 1e-5 ROFF = VON = -4 VOFF= -9).

10 MODEL S2 AMOD VSWITCH (RON = 1e-5 ROFF = VON = 0 VOFF= ).MODEL S2 BMOD VSWITCH (RON = 1e-5 ROFF = VON = VOFF= 0).ENDSNOTE: For further discussion of the PSPICE model, consult A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global Temperature Options; IEEE Power Electronics Specialist Conference Records, 1991, written by William J. Hepp and C. Frank +-68+-551+-198+-171868+-58+-RBREAKRVTEMP VBATRVTHRESIT17181922121315S1AS1BS2AS2 BCACBEGSEDS1481381413 MWEAKEBREAKDBODYRSOURCESOURCE1173 LSOURCERLSOURCECINRDRAINEVTHRES16218 MMEDMSTRODRAIN2 LDRAINRLDRAINDBREAKDPLCAPESLCRSLC1105515 0 RSLC21 GATERGATEEVTEMP9 ESGLGATERLGATE20+-+-+-6 hrf3205 , HRF3205S 2001 Fairchild Semiconductor CorporationHRF3205, HRF3205S Rev. BSPICE Thermal Model REV 25 July 97 hrf3205 CTHERM1 7 6 6 5 5 4 4 3 3 2 2 1 7 6 6 5 5 4 4 3 3 2 2 1 , hrf3205 SDISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHERNOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN.