Transcription of Low-Noise Two-Channel 100-MHz Clock Generator …

1 CDCM9102100 MHz LVPECLCDCUN1208 LPVDD25 MHzHCSL inputHCSL outputVDD150 56 471 471 Up to 8x100 MHzHCSL outputs150 56 ITTPOTTPIN1 PIN1 NOUT1 POUT1 NOUT2 POUT2 NOUT3 POUT3 NOUT4 POUT4 NOUT8 POUT8 NCopyright 2016, Texas Instruments IncorporatedProductFolderSample &BuyTechnicalDocumentsTools &SoftwareSupport &CommunityReferenceDesignAn IMPORTANTNOTICEat the end of this datasheetaddressesavailability,warranty, changes,use in safety-criticalapplications,intellectual propertymattersand FEBRUARY2012 REVISEDAPRIL2016 CDCM9102 Low-NoiseTwo-Channel100-MHzClock Generator11 Features1 IntegratedLow-NoiseClockGeneratorIncludi ngPLL,VCO,and LoopFilter Two Low-Noise100-MHzClocks(LVPECL,LVDS,or pair of LVCMOS) Supportfor HCSLS ignalingLevels(AC-Coupled) TypicalPeriodJitter:21 ps pk-pk TypicalRandomJitter.

2 510 fs RMS OutputTypeSet by Pins BonusSingle-Ended25-MHzOutput IntegratedCrystalOscillatorInputAccepts2 5-MHzCrystal OutputEnablePin ShutsOff Deviceand Outputs 5-mm 5-mm32-PinVQFNP ackage ESDP rotectionExceeds2000V HBM,500 VCDM IndustrialTemperatureRange( 40 C to 85 C) Applications ReferenceClockGenerationfor PCI ExpressGen 1, Gen 2, and Gen 3 General-PurposeClocking3 DescriptionTheCDCM9102is a low-jitterclockgeneratordesignedtoprovid ereferenceclocksforcommunicationsstandar dssuchas PCI Express .The devicesupportsup to PCIEgen3and is theseportsincludeLVPECL,LVDS,ora pairof outputbuffertype desiredby ,a single-ended25-MHzclockoutputportis thisportincludegeneral-purposeclocking,c lockingEthernetPHYs,or providinga referenceclockfor clocksgeneratedare derivedfroma (1)PARTNUMBERPACKAGEBODYSIZE(NOM)CDCM910 2 VQFN(32) (1) For all availablepackages,see the orderableaddendumatthe end of the FEBRUARY2012.

3 CDCM9102 SubmitDocumentationFeedbackCopyright 2012 2016,TexasInstrumentsIncorporatedTableof Contents1 Pin Configurationand Applicationand Deviceand Mechanical,Packaging,and RevisionHistoryNOTE:Pagenumbersfor previousrevisionsmay differfrompagenumbersin the (February2012)to RevisionAPage AddedESDR atingstable,FeatureDescriptionsection,De viceFunctionalModes,Applicationand Implementationsection,PowerSupplyRecomme ndationssection,Layoutsection,Deviceand DocumentationSupportsection,andMechanica l,Packaging,and Addedtext toDescription: The devicesupportsup to PCIEgen3and is ..1 Changedpart numberto Changedpart numberto Addedtext and Figure16 toPCI VDD423 OSCOUT2 OUT1N26NC15 NC22 GND3 OUT1P27NC14 GND21 XIN4 VDD128NC13 NC20 VDD65 OUT0N29NC12 RESET19 REGCAP16 OUT0P30NC11 OS018 VDD57OE31NC10 OS117 REGCAP28NC32NC9 FEBRUARY2012 REVISEDAPRIL2016 ProductFolderLinks.

4 CDCM9102 SubmitDocumentationFeedbackCopyright 2012 2016,TexasInstrumentsIncorporated5 DeviceComparisonTablePACKAGEDDEVICESFEAT URESTACDCM9102 RHBT32-pinVQFN(RHB)package,smalltapeand reel 40 C to 85 CCDCM9102 RHBR32-pinVQFN(RHB)package,tapeand reel(1)G = Ground,I = Input,O = Output,P = Power6 Pin Configurationand FunctionsRHBP ackage32-PinVQFN(TopView)Pin FunctionsPINTYPE(1) ,14, 22 GPowersupplygroundand thermalreliefREGCAP119 PCapacitorfor internalregulator,connect10- F Y5V capacitorto GNDREGCAP217 PCapacitorfor internalregulator,connect10- F Y5V capacitorto GNDVDD14 PPowerSupply,OUT0clockportVDD21 PPowerSupply,OUT1clockportVDD39 PPowersupply,low-noiseclockgeneratorVDD4 16 PPowersupply,low-noiseclockgeneratorVDD5 18 PPowersupply,low-noiseclockgeneratorVDD6 20 PPowersupply,crystaloscillatorinput4 CDCM9102 SCAS922A FEBRUARY2012 :CDCM9102 SubmitDocumentationFeedbackCopyright 2012 2016,TexasInstrumentsIncorporatedPin Functions(continued)PINTYPE(1)DESCRIPTIO NNAMENO.

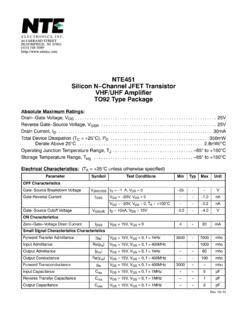

5 (2)For properdevicestartup,it is recommendedthat a capacitorbe installedfrompin 12 to , 13, 15, 24 32 No connectionpermittedOE7 OOutputenable/shutdowncontrolinput(seeTa ble2)OS110 OOutputformatselectcontrolinputs(seeTabl e3)OS011 OOutputformatselectcontrolinputs(seeTabl e3)RESET12 IDeviceresetinput(active-low)(seeTable4) (2)CRYSTALOSCILLATORXIN21 IParallelresonantcrystalinput(25 MHz)DEVICEOUTPUTSOSCOUT23 OOscillatoroutputport (25 MHz)OUT0N5 OOutput0 negativeterminal(100 MHz)OUT0P6 OOutput0 positiveterminal(100 MHz)OUT1N2 OOutput1 negativeterminal(100 MHz)OUT1P3 OOutput1 positiveterminal(100 MHz) FEBRUARY2012 REVISEDAPRIL2016 ProductFolderLinks:CDCM9102 SubmitDocumentationFeedbackCopyright 2012 2016,TexasInstrumentsIncorporated(1)Stre ssesbeyondthoselistedunderAbsoluteMaximu mRatingsmay causepermanentdamageto the stressratingsonly,whichdo not implyfunctionaloperationof the deviceat theseor any otherconditionsbeyondthoseindicatedunder RecommendedOperatingConditions.

6 Exposureto absolute-maximum-ratedconditionsfor extendedperiodsmay affectdevicereliability.(2)Supplyvoltage smustbe appliedsimultaneously.(3)The inputand outputnegativevoltageratingsmay be exceededif the inputand outputclamp currentratingsare observed7 (unlessotherwisenoted)(1)MINMAXUNITIINI nputcurrent20mAIOUTO utputcurrent50mAVDDxSupplyvoltage(2) (3) + (3) + CTstgStoragetemperature 65150 C(1)JEDEC documentJEP155statesthat 500-VHBM allowssafe manufacturingwith a standardESDcontrolprocess.(2)JEDEC documentJEP157statesthat 250-VCDM allowssafe manufacturingwith a (ESD)ElectrostaticdischargeHuman-bodymod el(HBM),per ANSI/ESDA/JEDECJS-001(1) 2000 VCharged-devicemodel(CDM),per JEDEC specificationJESD22-C101(2) 4085 C(1)For moreinformationabouttraditionaland new thermalmetrics,see theSemiconductorand IC PackageThermalMetricsapplicationreport,S PRA953.

7 (2)4 4 Viason (1)(2)CDCM9102 UNITRHB(VQFN)32 PINSR C/WR JC(top)Junction-to-case(top) C/WR C/W C/W JBJunction-to-boardcharacterizationparam eter2 C/WR JC(bot)Junction-to-case(bottom) C/W6 CDCM9102 SCAS922A FEBRUARY2012 :CDCM9102 SubmitDocumentationFeedbackCopyright 2012 2016,TexasInstrumentsIncorporated(1)LVCM OS inputsat TA= 40 C to 85 C(2)Crystalcharacteristicsfor external25 MHzcrystalwith VDD= V, TA= 40 C to 85 C(3)Clockoutputbufferwith outputmode= LVPECLat VDD1,VDD2= V; TA= 40 C to 85 C(4)Clockoutputbufferwith outputmode= LVDSat VDD1,VDD2= V; TA= 40 C to 85 C(5)Clockoutputbufferwith outputmode= LVCMOSat VDD1,VDD2= V; TA= 40 C to 85 (unlessotherwisenoted)PARAMETERTESTCONDI TIONSMINTYPMAXUNITLVCMOSINPUTS(1)VIHI nputhigh VDDVVILI nputlow VDDVIIHI nputhigh currentVDD= V, VIL= 0 V200 AIILI nputlow currentVDD= 3 V, VIH= V 200 ACINI nputcapacitance810pFRPUI nputpullupresistor150k CRYSTALCHARACTERISTICS(XIN)(2)fXTALC rystalinputfrequencyFundamentalmode25 MHzESRE ffectiveseriesresistanceofcrystal50 CINOn-chipload capacitance810pFXTALDLM aximumdrivelevel- (OUTPUTMODE= LVPECL)(3)

8 VOHO utputhigh voltageVDD voltageVDD 2 VDD |VOD| tFOutputrise and fall time20%to 80%175psODCO utputduty cycle45%55%tSKEWS kewbetweenoutputs20psCLOCKOUTPUTBUFFER(O UTPUTMODE= LVDS)(4)|VOD| VOSVOS magnitudechange50mVtRand tFOutputrise and fall time20%to 80%255psODCO utputduty cycle45%55%tSKEWS kewbetweenoutputs30psCLOCKOUTPUTBUFFER(O UTPUTMODE= LVCMOS)(5)VOHO utputhigh voltageVCC= 3 V to V, IOH= 100 AVDD voltageVCC= 3 V to V, IOH= 100 80% cycle45%55% FEBRUARY2012 REVISEDAPRIL2016 ProductFolderLinks:CDCM9102 SubmitDocumentationFeedbackCopyright 2012 2016, 100 MHz,VDD= V, TA= 25 C, and jitter integrationbandwidthbetween10 kHz and 20 MHz(unlessotherwisenoted)MINTYPMAXUNITLV CMOSOUTPUTMODER andomjitter507fs pk-pkLVPECLOUTPUTMODER andomjitter510fs pk-pkLVDSOUTPUTMODER andomjitter533fs CDCM9102 TypicalPhaseNoisePerformance(LVPECLMode) LVPECL150(2)WPhase Noise AnalyzerRF50W50 WOscilloscopeCH1CH2 LVPECL50W50W50(2)WV- 2 VDDLVCMOS50 WPhase Noise AnalyzerRF50 WLVCMOS5 pF8 CDCM9102 SCAS922A FEBRUARY2012 :CDCM9102 SubmitDocumentationFeedbackCopyright 2012 2016,TexasInstrumentsIncorporated8 LVCMOSO utputTestLoadFigure3.

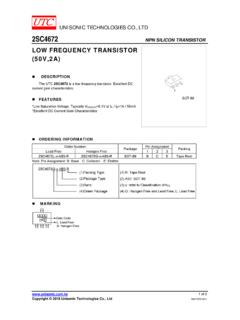

9 LVCMOSAC Configurationfor DeviceTestFigure4. LVPECLDC Configurationfor DeviceTestFigure5. LVPECLAC Configurationfor DeviceTestLVDSP hase Noise FEBRUARY2012 REVISEDAPRIL2016 ProductFolderLinks:CDCM9102 SubmitDocumentationFeedbackCopyright 2012 2016,TexasInstrumentsIncorporatedTestCon figurations(continued)Figure6. LVDSDC Configurationfor DeviceTestFigure7. LVDSAC Configurationfor DeviceTestXO25 MHzCSTRAYCPARASITICCLCINXIN(Pin 21)OS0OS1 CDCM9102 XOLowNoiseClockGeneratorRESETOEOSCOUTOUT 1 POUT1 NOUT0 POUT0 NREGCAP1 REGCAP2 Copyright 2016, Texas Instruments IncorporatedVregVreg10 CDCM9102 SCAS922A FEBRUARY2012 :CDCM9102 SubmitDocumentationFeedbackCopyright 2012 2016,TexasInstrumentsIncorporated9 CDCM9102is a high-performancePLL that generates2 copiesof commonly-usedreferenceclockswith lessthan1-psRMSjitter froma on-chipPLLwithan a crystalinputinterface,a phasefrequencydetector(PFD),a chargepump,an on-chiploopfilter,and prescalerand CDCM9102deviceare the outputdividerand PLLandoutputdividerare pre-programmedto generate2 copiesof 100 MHzin LVCMOS,LVPECLor PLL is poweredby on-chip,low-dropout(LDO)

10 Regulatedsupplynetworkispartitionedsucht hat the sensitiveanalogsuppliesare poweredfromseparateLDOsratherthanthe digitalsupplieswhichuse a the PLL fromany noisein theexternalpower-supplyrail. The REG_CAP1and REG_CAP2pins shouldeachbe connectedto groundby 10- Fcapacitorsto (XIN)InterfaceThe CDCM9102implementsaColpittsoscillator; therefore,one side of the crystalconnectsto the XIN pin andthe othercrystalterminalconnectsto devicerequiresthe use of a fundamental-modecrystal,andthe oscillatoroperatesin correctloadcapacitanceis necessaryto ensurethat loadcapacitancecomprisesall capacitancesin the oscillatorfeedbackloop(thecapacitancesse enbetweenthe terminalsof the crystalin the circuit).