Transcription of 74HC595 8−Bit Serial−Input/Serial or …

1 Semiconductor Components Industries, LLC, 2007 March, 2007 Rev. 11 Publication Order Number: 74HC595 /D74HC5958 Bit Serial Input/Serial orParallel Output ShiftRegister with Latched3 State OutputsHigh Performance Silicon Gate CMOSThe 74HC595 consists of an 8 bit shift register and an 8 bit D typelatch with three state parallel outputs. The shift register accepts serialdata and provides a serial output. The shift register also providesparallel data to the 8 bit latch. The shift register and latch haveindependent clock inputs. This device also has an asynchronous resetfor the shift HC595 directly interfaces with the SPI serial data port onCMOS MPUs and Output Drive Capability: 15 LSTTL Loads Outputs Directly Interface to CMOS, NMOS, and TTL Operating Voltage Range: to V Low Input Current: mA High Noise Immunity Characteristic of CMOS Devices In Compliance with the Requirements Defined by JEDECS tandard No.

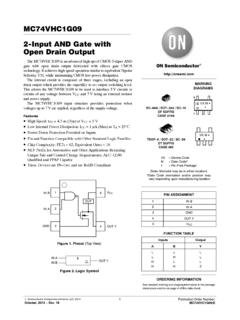

2 7A ESD Performance: HBM > 2000 V; Machine Model > 200 V Chip Complexity: 328 FETs or 82 Equivalent Gates Improvements over HC595 Improved Propagation Delays 50% Lower Quiescent Power Improved Input Noise and Latchup Immunity These are Pb Free Device CodeA= Assembly LocationL, WL= Wafer LotY, YY= YearW, WW= Work WeekG or = Pb Free PackageSee detailed ordering and shipping information in the packagedimensions section on page 2 of this data INFORMATIONSOIC 16D SUFFIXCASE 751 BTSSOP 16DT SUFFIXCASE 948F116116HC595 ALYW 116116HC595 GAWLYWW(Note: Microdot may be in either location) 74HC595 DIAGRAMSERIALDATAINPUT1411101213 SHIFTCLOCKRESETLATCHCLOCKOUTPUTENABLESHI FTREGISTERLATCH1512345679 QAQBQCQDQEQFQGQHSQHAVCC = PIN 16 GND = PIN 8 PARALLELDATAOUTPUTSSERIALDATAOUTPUTPIN ASSIGNMENT13141516910111254321876 LATCH CLOCKOUTPUT ENABLEAQAVCCSQHRESETSHIFT CLOCKQEQDQCQBGNDQHQGQFORDERING INFORMATIOND evicePackageShipping 74HC595DR2 GSOIC 16(Pb Free)2500 Tape & Reel74HC595 DTR2 GTSSOP 16*2500 Tape & Reel For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel PackagingSpecifications Brochure, BRD8011/D.

3 *This package is inherently Pb MAXIMUM RATINGSS ymbolParameterValueUnitVCCDC Supply Voltage (Referenced to GND) to + Input Voltage (Referenced to GND) to VCC + Output Voltage (Referenced to GND) to VCC + Input Current, per Pin 20mAIoutDC Output Current, per Pin 35mAICCDC Supply Current, VCC and GND Pins 75mAPDP ower Dissipation in Still Air,SOIC Package TSSOP Package 500450mWTstgStorage Temperature 65 to + 150 CTLLead Temperature, 1 mm from Case for 10 Seconds(SOIC or TSSOP Package)260 CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stressratings only. Functional operation above the Recommended Operating Conditions is not exposure to stresses above the Recommended Operating Conditions may affect devicereliability.

4 Derating SOIC Package: 7 mW/ C from 65 to 125 CTSSOP Package: mW/ C from 65 to 125 CFor high frequency or heavy load considerations, see Chapter 2 of the ON Semiconductor High Speed CMOS Data Book (DL129/D).RECOMMENDED OPERATING CONDITIONSS ymbolParameterMinMaxUnitVCCDC Supply Voltage (Referenced to GND) , VoutDC Input Voltage, Output Voltage(Referenced to GND)0 VCCVTAO perating Temperature, All Package Types 55+ 125 Ctr, tfInput Rise and Fall TimeVCC = V(Figure 1)VCC = VVCC = V0001000500400nsThis device contains protectioncircuitry to guard against damagedue to high static voltages or electricfields. However, precautions mustbe taken to avoid applications of anyvoltage higher than maximum ratedvoltages to this high impedance cir-cuit.

5 For proper operation, Vin andVout should be constrained to therange GND v (Vin or Vout) v inputs must always betied to an appropriate logic voltagelevel ( , either GND or VCC).Unused outputs must be left ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)SymbolParameterTest ConditionsVCC(V)Guaranteed LimitUnit 55 to 25 Cv 85 Cv 125 CVIHM inimum High Level InputVoltageVout = V or VCC V|Iout| v 20 Low Level InputVoltageVout = V or VCC V|Iout| v 20 High Level OutputVoltage, QA QHVin = VIH or VIL|Iout| v 20 = VIH or VIL|Iout| v mA|Iout| v mA|Iout| v Low Level OutputVoltage, QA QHVin = VIH or VIL|Iout| v 20 = VIH or VIL|Iout| v mA|Iout| v mA|Iout| v High Level OutputVoltage, SQHVin = VIH or VILIIoutI v 20 = VIH or VIL|Iout| v mAIIoutI v mA IIoutIv Low Level OutputVoltage.

6 SQHVin = VIH or VILIIoutI v 20 = VIH or VIL|Iout| v mAIIoutI v mA IIoutIv Input LeakageCurrentVin = VCC or Three StateLeakageCurrent, QA QHOutput in High Impedance StateVin = VIL or VIHVout = VCC or Quiescent SupplyCurrent (per Package)Vin = VCC or GNDlout = 0 : Information on typical parametric values can be found in Chapter 2 of the ON Semiconductor High Speed CMOS Data Book(DL129/D). 74HC595 ELECTRICAL CHARACTERISTICS (CL = 50 pF, Input tr = tf = ns)SymbolParameterVCC(V)Guaranteed LimitUnit 55 to 25 Cv 85 Cv 125 CfmaxMaximum Clock Frequency (50% Duty Cycle)(Figures 1 and 7) ,tPHLM aximum Propagation Delay, Shift Clock to SQH(Figures 1 and 7) Propagation Delay, Reset to SQH(Figures 2 and 7) ,tPHLM aximum Propagation Delay, Latch Clock to QA QH(Figures 3 and 7) ,tPHZM aximum Propagation Delay, Output Enable to QA QH(Figures 4 and 8) ,tPZHM aximum Propagation Delay, Output Enable to QA QH(Figures 4 and 8) ,tTHLM aximum Output Transition Time, QA QH(Figures 3 and 7) ,tTHLM aximum Output Transition Time, SQH(Figures 1 and 7)

7 Input Capacitance 101010pFCoutMaximum Three State Output Capacitance (Output inHigh Impedance State), QA QH 151515pFNOTE: For propagation delays with loads other than 50 pF, and information on typical parametric values, see Chapter 2 of the ONSemiconductor High Speed CMOS Data Book (DL129/D).CPDP ower Dissipation Capacitance (Per Package)*Typical @ 25 C, VCC = VpF300* Used to determine the no load dynamic power consumption: PD = CPD VCC2f + ICC VCC. For load considerations, see Chapter 2 of theON Semiconductor High Speed CMOS Data Book (DL129/D). 74HC595 REQUIREMENTS (Input tr = tf = ns)SymbolParameterVCC(V)Guaranteed LimitUnit25 C to 55 Cv 85 Cv 125 CtsuMinimum Setup Time, Serial Data Input A to Shift Clock(Figure 5) Setup Time, Shift Clock to Latch Clock(Figure 6) Hold Time, Shift Clock to Serial Data Input A(Figure 5) Recovery Time, Reset Inactive to Shift Clock(Figure 2) Pulse Width, Reset(Figure 2) Pulse Width, Shift Clock(Figure 1) Pulse Width, Latch Clock(Figure 6) , tfMaximum Input Rise and Fall Times(Figure 1)

8 TABLEO perationInputsResulting FunctionResetSerialInputAShiftClockLatch ClockOutputEnableShiftRegisterContentsLa tchRegisterContentsSerialOutputSQHP arallelOutputsQA QHReset shift registerLXXL, H, LLULUS hift data into shiftregisterHD L, H, LD SRA;SRN SRN+1 USRG SRHUS hift register remainsunchangedHXL, H, L, H, LUUUUT ransfer shift registercontents to latchregisterHXL, H, LUSRN LRNUSRNL atch register remainsunchangedXXXL, H, L*U*UEnable parallel outputsXXXXL**EnabledForce outputs into highimpedance stateXXXXH**ZSR = shift register contentsD = data (L, H) logic level = Low to High* = depends on Reset and Shift Clock inputsLR = latch register contentsU = remains unchanged = High to Low** = depends on Latch Clock inputPIN DESCRIPTIONSINPUTSA (Pin 14)Serial Data Input.

9 The data on this pin is shifted into the8 bit serial shift INPUTSS hift Clock (Pin 11)Shift Register Clock Input. A low to high transition onthis input causes the data at the Serial Input pin to be shiftedinto the 8 bit shift (Pin 10)Active low, Asynchronous, Shift Register Reset Input. Alow on this pin resets the shift register portion of this deviceonly. The 8 bit latch is not Clock (Pin 12)Storage Latch Clock Input. A low to high transition onthis input latches the shift register Enable (Pin 13)Active low Output Enable. A low on this input allows thedata from the latches to be presented at the outputs. A highon this input forces the outputs (QA QH) into thehigh impedance state.

10 The serial output is not affected bythis control QH (Pins 15, 1, 2, 3, 4, 5, 6, 7)Noninverted, 3 state, latch (Pin 9)Noninverted, Serial Data Output. This is the output of theeighth stage of the 8 bit shift register. This output does nothave three state WAVEFORMSSERIALINPUT A50%50%SWITCHCLOCKVCCGNDVALID tsuthFigure QHOUTPUTS50%tPLHtPHLtTLHtTHL90%50%10%VCC GNDVCCGNDSHIFTCLOCKLATCHCLOCKF igure QOUTPUT Q50%50%90%10%tPZLtPLZtPZHtPHZVCCGNDHIGHI MPEDANCEVOLVOHHIGHIMPEDANCEOUTPUTENABLE5 0%TEST CIRCUITS*Includes all probe and jig capacitanceCL*TEST POINTDEVICEUNDERTESTOUTPUT*Includes all probe and jig capacitanceCL*TEST POINTDEVICEUNDERTESTOUTPUTCONNECT TO VCC WHENTESTING tPLZ AND TO GND WHENTESTING tPHZ AND kWFigure LOGIC DIAGRAMOUTPUTENABLELATCHCLOCKSERIALDATAI NPUT ASHIFTCLOCKRESET13121411101512345679 QAQBQCQDQEQFQGQHSERIALDATAOUTPUT SQHPARALLELDATAOUTPUTS74HC595